- polski

-

EnglishDeutschItaliaFrançais한국의русскийSvenskaNederlandespañolPortuguêspolski繁体中文SuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикGalegolietuviųMaoriRepublika e ShqipërisëالعربيةአማርኛAzərbaycanEesti VabariikEuskeraБеларусьLëtzebuergeschAyitiAfrikaansBosnaíslenskaCambodiaမြန်မာМонголулсМакедонскиmalaɡasʲພາສາລາວKurdîსაქართველოIsiXhosaفارسیisiZuluPilipinoසිංහලTürk diliTiếng ViệtहिंदीТоҷикӣاردوภาษาไทยO'zbekKongeriketবাংলা ভাষারChicheŵaSamoa日本語SesothoCрпскиKiswahiliУкраїнаनेपालीעִבְרִיתپښتوКыргыз тилиҚазақшаCatalàCorsaLatviešuHausaગુજરાતીಕನ್ನಡkannaḍaमराठी

Wyjaśnienie ASIC: projekt, typy i porównanie procesorów graficznych

Katalog

Odkrywanie chipów ASIC w 2026 roku

Układy scalone specyficzne dla aplikacji (ASIC) oznaczają głębokie odejście od wszechstronnych procesorów ogólnego przeznaczenia na rzecz wydajnego wykonywania precyzyjnych zadań.Do roku 2026 ASIC będą dominujące w różnych kluczowych branżach, takich jak generatywna sztuczna inteligencja (GenAI), systemy kryptograficzne i technologie motoryzacyjne.Napędzają innowacje, zapewniając niezrównaną prędkość wykonywania wyspecjalizowanych algorytmów, takich jak mnożenie macierzy stosowane w sieciach neuronowych, dzięki czemu pozycjonują się jako niezrównane narzędzia w scenariuszach wymagających dużej wydajności.

Te celowe obwody prezentują wyjątkowe możliwości w ekosystemach intensywnie przetwarzających dane, gdzie dokładność i wydajność obliczeń są najważniejsze.Wielkoskalowe modele języka naturalnego, które stanowią podstawę znacznego postępu w GenAI, uosabiają ten potencjał.Układy ASIC z łatwością przetwarzają rozległe i skomplikowane operacje, umożliwiając przełomowe zastosowania w takich obszarach, jak tłumaczenie w czasie rzeczywistym lub generowanie kreatywnych treści, które na nowo definiują doświadczenia.

Postępy w produkcji układów ASIC na nowo zdefiniowały innowacje w półprzewodnikach, począwszy od uznanych węzłów 5 nm po najnowocześniejsze tranzystory Gate-All-Around wykonane w procesie 2 nm.Godną uwagi cechą tych zmian jest rosnące przyjęcie architektur chipletów.Te wzajemnie połączone moduły ujednolicają funkcje, takie jak obliczenia, pamięć i wejście/wyjście za pośrednictwem ultraszybkich połączeń wzajemnych, wykazując się zarówno pomysłowością techniczną, jak i praktycznym zastosowaniem.

Kluczowe komponenty technologiczne wzmacniają siłę układów ASIC:

• Pamięć o dużej przepustowości (HBM3e), która gwarantuje szybki dostęp do danych w wymagających warunkach.

• Wbudowane systemy zarządzania energią, strategicznie zaprojektowane w celu minimalizacji wydatków na energię podczas zadań wymagających dużej wydajności.

• Wbudowane protokoły bezpieczeństwa zwiększające ochronę wrażliwych danych, szczególnie istotne w zastosowaniach takich jak systemy kryptograficzne.

Takie zróżnicowane rozważania przy projektowaniu układów ASIC ilustrują połączenie inżynierii precyzyjnej z praktycznym wdrożeniem, umożliwiając tworzenie kompaktowych, ale wydajnych platform obliczeniowych.

Wdrożenie układów ASIC nabiera tempa, ponieważ wyzwania takie jak stagnacja prawa Moore'a utrudniają skalowanie tradycyjnych procesorów.Poszukiwanie przełomowych innowacji skłania do wykorzystania układów ASIC, które wyróżniają się skalowalnością, efektywnością energetyczną i stabilnością operacyjną.

Układy ASIC w dużej mierze zawdzięczają swoją sprawność kooptymalizacji sprzętu i oprogramowania.Osadzając logikę specyficzną dla aplikacji bezpośrednio w krzemie, chipy te osiągają znaczną redukcję opóźnień, zmniejszają zużycie energii i utrzymują niezrównaną niezawodność.Ta harmonijna integracja zapewnia niezaprzeczalne korzyści kompleksowym systemom, takim jak modemy 5G, silniki wnioskowania AI i pojazdy autonomiczne.Stanowi dowód na to, jak dostosowana do indywidualnych potrzeb precyzja projektowania może przekształcić zorientowane na cel wyniki w rzeczywistość.

ASIC zmieniają krajobraz operacyjny w wielu branżach.W technologii motoryzacyjnej chipy te umożliwiają pojazdom autonomicznym podejmowanie decyzji w czasie rzeczywistym.Obsługując dane sensoryczne za pomocą precyzyjnie dostrojonych obliczeń sieci neuronowej, zapewniają bezproblemowe działanie nawet przy rygorystycznych ograniczeniach dotyczących opóźnień lub obciążenia obliczeniowego.

W systemach kryptograficznych układy ASIC umożliwiają szybkie i bezpieczne uwierzytelnianie transakcji, zwiększając wydajność sieci blockchain.Jednocześnie rozwijająca się dziedzina przetwarzania brzegowego czerpie znaczne korzyści z wdrożenia układów ASIC.Kompaktowe, energooszczędne chipy zapewniają zaawansowaną moc obliczeniową zdecentralizowanym urządzeniom, umożliwiając zastosowanie w takich obszarach, jak predykcyjna konserwacja przemysłowa i spersonalizowana analityka w służbie zdrowia.Integracja ta stanowi podstawę odważnej redefinicji wzajemnego oddziaływania pomiędzy mocą, przenośnością i precyzją, demonstrując potencjał solidnego, zlokalizowanego przetwarzania w miniaturowych obudowach.

Innowacje ASIC uosabiają zwrot w kierunku rozwiązań, które zaspokajają specyficzne wymagania o wysokim priorytecie.Skupienie się na projektowaniu na zamówienie pokazuje, jak specjalizacja konsekwentnie przewyższa uogólnienie w technologiach o znaczeniu krytycznym.Uderzający wniosek polega na tym, jak postępy w układach ASIC łączą się z równoległym postępem w optymalizacji oprogramowania i algorytmów, podkreślając wzajemnie korzystny cykl wzrostu.

Delikatna równowaga między wydajnością, miniaturyzacją i wydajnością oddaje istotę przełomów inżynieryjnych, a postępy te inspirują bezprecedensową współpracę między dyscyplinami.Stawiając na pierwszym miejscu korzyści ukierunkowane na zastosowania bez nadwyżki, układy ASIC udoskonalają swoją pozycję jako szkieletu niezliczonych technologii transformacyjnych.

Przebieg pracy w projekcie ASIC

Rozwój układów ASIC w 2026 r. uwzględnił przełomowy wpływ narzędzi do automatyzacji projektowania elektronicznego (EDA) opartych na sztucznej inteligencji.Narzędzia te zapewniają przyspieszenie i dokładność procesu projektowania, zwłaszcza na etapach optymalizacji, takich jak rozmieszczanie i wyznaczanie tras, aby sprostać rosnącej złożoności elektroniki nowej generacji.Podróż projektowa ASIC składa się z wielu etapów, które wymagają skupienia, pomysłowych strategii i mistrzostwa w danej dziedzinie.

Na etapie architektonicznym chip jest podzielony na integralne komponenty funkcjonalne, w tym między innymi rdzenie AI, kontrolery pamięci i interfejsy sieciowe.Cele dotyczące zużycia energii, wydajności i rozmiaru są dostosowane do praktycznych potrzeb i standardów branżowych.

• Kompromisy w zakresie mocy, wydajności i powierzchni wpływają na ogólne działanie chipa.Energooszczędne projekty urządzeń brzegowych wymagają starannego dostrojenia, aby utrzymać prędkość przetwarzania.

• Obserwacje empiryczne pokazują, że spójna współpraca zachęca do iteracyjnego udoskonalania.Takie procesy mają na celu przewidywanie wyzwań i stawienie im czoła, począwszy od regulacji termicznej w akceleratorach AI po mechanizmy skalowania adaptacyjnego we wdrożeniach centrów danych, przed głębszymi etapami rozwoju.

Faza projektowania logiki koncentruje się na określeniu zamierzonej funkcjonalności chipa za pomocą języków opisu sprzętu (HDL), takich jak Verilog i VHDL.To działanie generuje abstrakcje poziomu transferu rejestru (RTL), które wyznaczają przepływ danych pomiędzy rejestrami i definiują zachowania logiczne.

• Wydajność dalszych procesów, takich jak synteza, w dużym stopniu zależy od spójności i zoptymalizowanej jakości projektów RTL.Nieefektywne konfiguracje stwarzają ryzyko rozprzestrzeniania się systemowych wąskich gardeł.

• Projektowanie modułowe jest obecnie powszechne i wykorzystuje sprawdzone biblioteki i moduły kodu, aby przyspieszyć projektowanie przy jednoczesnym zachowaniu jakości.W systemach o wysokiej wydajności na poziomie RTL dodano obwody sprawdzające błędy i logikę samoregulującą, aby chronić działanie podczas dużych obciążeń.

Weryfikacja jest niezastąpioną bramką, dzięki której hipotezy projektowe poddawane są rygorystycznym testom pod kątem błędów w wielu wymiarach, termicznym, elektrycznym i obliczeniowym.Narzędzia takie jak systemy emulacji oparte na FPGA i konfiguracje cyfrowych bliźniaków odgrywają zasadniczą rolę w ocenie zachowania układów ASIC w warunkach praktycznych.

• Rozszerzono scenariusze walidacji, aby dopasować je do różnych warunków pracy i ujawnić przypadki brzegowe.Układy ASIC wysokiej częstotliwości do przetwarzania danych wymagają rygorystycznych kontroli stabilności sygnału pod wpływem zmian temperatury i napięcia.

• Przepływy pracy weryfikacyjne wykorzystują symulacje do analizy ruchu, koordynacji i interakcji pomiędzy podzespołami w chipach podczas zadań przetwarzania danych na dużą skalę.Zapewnia to spójną funkcjonalność przed rozpoczęciem zmian produkcyjnych.

Faza projektowania fizycznego przechodzi od abstrakcyjnych konstrukcji logicznych do układów materialnych wypełnionych skomplikowanymi sieciami tranzystorów.Wykorzystując najnowocześniejsze węzły produkcyjne, takie jak technologie 3 nm, w uznanych odlewniach, osiąga się niespotykaną gęstość przy jednoczesnym zachowaniu wydajności energetycznej.

• Skoordynowane interakcje między zespołami projektowymi i produkcyjnymi w coraz większym stopniu opierają się na algorytmach optymalizacji, dostosowanych do łagodzenia wyzwań, takich jak nadmierny upływ mocy lub opóźnienia w przewodach w złożonych układach.Informacje zwrotne między zespołami zajmującymi się rozwojem i produkcją poprawiają konfiguracje w celu zapewnienia lepszej kompatybilności litograficznej.

• Równolegle poszukuje się dodatkowych podejść eksperymentalnych, obejmujących alternatywne konfiguracje i adaptacje do określonych ograniczeń węzła, w celu lepszej integracji ze stale rozwijającymi się metodologiami produkcji.

Kulminacją cyklu życia ASIC jest faza rozklejania, konsolidująca szczegółowe plany projektowe na potrzeby wdrożenia produkcyjnego.Zaawansowane praktyki produkcyjne, takie jak fotolitografia w połączeniu z najnowocześniejszymi technologiami opakowań heterogenicznych, takimi jak 2,5D CoWoS, stanowią podstawę produkcji fizycznej.

• Surowe protokoły inspekcji wdrażane przez zespoły produkcyjne potwierdzają zgodność z pierwotnymi zaleceniami projektowymi.Informacje zwrotne generowane w wyniku tych ocen często wracają do iteracji projektu, służąc jako podstawa dla przyszłych ulepszeń.

• Wydajność i precyzja obserwowane podczas cykli produkcyjnych znajdują bezpośrednie zastosowanie w dziedzinach wymagających niezawodności przy dużych obciążeniach obliczeniowych, co widać w infrastrukturze sztucznej inteligencji i platformach obliczeniowych o wysokiej wydajności.

Iteracyjny postęp obserwowany w rozwoju ASIC kładzie nacisk na dążenie do udoskonalonych wskaźników PPA dostosowanych do praktycznego znaczenia i doskonałości wydajności.Etapy obejmujące analizę architektoniczną, logiczny montaż i skomplikowaną fizyczną produkcję stanowią przykład połączenia kreatywności technicznej i empirycznej precyzji charakteryzującej nowoczesne przepływy pracy ASIC.

Łącząc innowacyjne metody ze zbiorową wiedzą, branża kontynuuje swój rozwój, dostarczając rozwiązania sprzętowe, które są wyjątkowo dostosowane do wymagań skalowalności, odporności operacyjnej i efektywności energetycznej w konkurencyjnych krajobrazach technologicznych.

Ocena układów ASIC w porównaniu z procesorami graficznymi: mocne strony i wyzwania

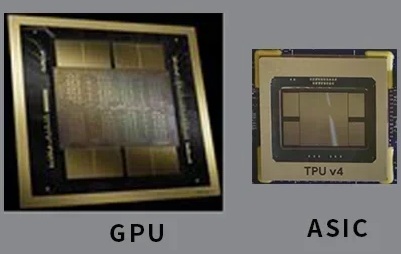

Układy scalone specyficzne dla aplikacji (ASIC) są przeznaczone do zadań jednofunkcyjnych i zawierają dedykowaną logikę sprzętową w celu wykonywania określonych operacji z dużą wydajnością.Natomiast jednostki przetwarzania grafiki (GPU) działają jak elastyczne, równoległe silniki obliczeniowe, doskonale radzące sobie z różnorodnymi i wymagającymi obciążeniami.Rozbieżność w ich filozofiach projektowania określa ich mocne strony i kompromisy, podkreślając decyzje wymagane przy wyborze pomiędzy dwiema technologiami.

Zalety układów ASIC

Układy ASIC z założenia optymalizują wydajność i zużycie energii dla określonych zastosowań, zapewniając wyniki niezrównane w przypadku specjalistycznych obciążeń.

• Dzięki wykluczeniu komponentów typowych dla układów ogólnego przeznaczenia, takich jak procesory i procesory graficzne, układy ASIC osiągają wyjątkową gęstość chipów.Pozwala to na nawet pięciokrotne zmniejszenie rozmiaru fizycznego w kluczowych zastosowaniach, takich jak sztuczna inteligencja.

• Centra danych wyposażone w układy ASIC odnotowują spadek zużycia energii, często wahający się od 50% do 70%.Redukcja ta doskonale wpisuje się w globalne wysiłki na rzecz wykorzystania systemów energooszczędnych i zmniejszenia śladu węglowego.

• Niższe zużycie energii przekłada się na praktyczne oszczędności i efektywność operacyjną, np. zmniejszone zapotrzebowanie na chłodzenie, mniej zasobów fizycznych na infrastrukturę i elastyczność w zakresie skalowania operacji.

Układy ASIC rozwiązują również problemy związane z opóźnieniami w czasie rzeczywistym:

• Unikając zewnętrznych operacji na pamięci, które mogą ograniczać wydajność procesora graficznego podczas wnioskowania w czasie rzeczywistym, układy ASIC zapewniają szybkość reakcji wymaganą w krytycznych aplikacjach.Na przykład branże uzależnione od pojazdów autonomicznych, systemów natychmiastowego wykrywania oszustw lub hiperinteraktywnych asystentów cyfrowych cenią sobie ten wzrost szybkości reakcji na poziomie mikrosekund.

Korzyści ekonomiczne pojawiają się wraz ze skalą produkcji ASIC:

• Chociaż początkowy rozwój jest kosztowny, produkcja na dużą skalę radykalnie zmniejsza koszty jednostkowe, a dojrzałe wdrożenia dają modele klasy konsumenckiej w cenie zaledwie 0,30 USD.To sprawia, że układy ASIC są szczególnie destrukcyjne dla branż zależnych od powtarzalnego uczenia maszynowego lub potoków wnioskowania.

Warto zauważyć, że specjaliści operacyjni w środowiskach chmurowych podkreślają praktyczne zalety stosowania układów AI ASIC.Systemy te wytwarzają mniej ciepła, wymagają mniejszej interwencji mechanicznej, dzięki czemu zespoły mogą skoncentrować się na wydłużonych cyklach innowacji lub skalowaniu infrastruktury w celu spełnienia przyszłych wymagań.

Wady układów ASIC

Rozwój ASIC stwarza przeszkody, które łagodzą jego skądinąd znaczące zalety, zwłaszcza pod względem kosztów, możliwości adaptacji i ryzyka logistycznego.

• Początkowe koszty opracowania zaawansowanych układów ASIC są wysokie i według prognoz wzrosną do 500 milionów dolarów do 2026 r. w przypadku najnowocześniejszych projektów. Tak wysokie bariery ograniczają dostęp do branż, które mogą uzasadniać produkcję na masową skalę w celu rozłożenia kosztów w czasie.

• Sukces we wdrażaniu sprzętu ASIC zależy od wiarygodnej prognozy popytu.Wymóg ten naraża organizacje na ryzyko związane z wahaniami rynków lub nagłymi zmianami w krajobrazie technologicznym, w przypadku których błędne obliczenia mogą sprawić, że znaczące inwestycje staną się niemożliwe do odzyskania.

Układy ASIC z natury nie mają zdolności do dynamicznej ewolucji:

• Kiedy algorytmy oprogramowania przekraczają możliwości wbudowane w projekt ASIC, podstawowy sprzęt często staje się nieistotny lub bezużyteczny.Natomiast procesory graficzne oferują możliwość dostosowania reprogramowalnych aktualizacji oprogramowania, aby dostosować się do szybko zmieniających się obciążeń.

• Sztywny, jednorazowy proces projektowania układów ASIC, trwający od 12 do 24 miesięcy, stanowi rozbieżność z branżami takimi jak gry czy badania nad sztuczną inteligencją, w których trendy technologiczne ewoluują w przyspieszonym tempie.Dla porównania, procesory graficzne poddawane są iteracyjnym aktualizacjom co kwartał, aby zachować zgodność z nowymi standardami branżowymi.

Kwestie logistyczne stwarzają dalsze komplikacje:

• Niepowodzenia lub przeszkody produkcyjne, takie jak spory dotyczące własności intelektualnej, mogą wykoleić harmonogram realizacji projektu.Nawet dobrze finansowane organizacje borykają się z opóźnieniami, które odbijają się na rurociągach produktów, zwiększając ryzyko projektów w branżach o rygorystycznych wymaganiach dotyczących dostaw.

Aplikacje

Czynniki odróżniające układy ASIC od procesorów graficznych wyraźnie widać w zastosowaniach praktycznych, gdzie ich wdrożenie zależy w dużym stopniu od konkretnych potrzeb zadania.

• Układy ASIC wyróżniają się, gdy są stosowane do powtarzalnych, wysoce przewidywalnych operacji, które wymagają minimalnej ewolucji w czasie.Przypadki użycia obejmują wydobywanie bitcoinów, wąsko ukierunkowane zadania wnioskowania AI i zoptymalizowane platformy przetwarzania brzegowego.

• Z kolei procesory graficzne dominują w środowiskach, w których najważniejsza jest elastyczność i innowacyjność.Należą do nich badania nad uczeniem maszynowym, eksperymenty eksploracyjne ze sztuczną inteligencją, złożone potoki renderowania i aplikacje wymagające uogólnionej mocy obliczeniowej.

Decyzja pomiędzy układami ASIC a procesorami graficznymi ujawnia delikatny taniec pomiędzy specjalizacją a możliwościami adaptacji.Organizacje oceniające te technologie muszą nie tylko wziąć pod uwagę punkty odniesienia dotyczące wydajności, ale także ocenić cechy ekonomiczne, rozwojowe i związane z cyklem życia, które definiują ich własną strategię branżową lub operacyjną.

U podstaw debaty ASIC kontra GPU rzuca światło na szerszy dialog technologiczny pomiędzy wydajnością i elastycznością.Ta dynamiczna zależność w dalszym ciągu kształtuje sposób, w jaki branże przekraczają granice, tworzą możliwości i dostosowują się do szybkiej ewolucji technologicznej.Zrozumienie tej równowagi zapewnia cenny wgląd w trajektorię współczesnego postępu obliczeniowego i ich rolę w kształtowaniu szerszego postępu społecznego.

Rodzaje architektur ASIC

Architektury ASIC można organizować w oparciu o metodologie projektowania lub obszary zastosowań.Klasyfikacje te zapewniają wgląd w zróżnicowane techniki inżynierii półprzewodników zaprojektowane w celu optymalizacji funkcjonalności chipów w różnych dziedzinach.Ostatnie osiągnięcia pokazują, że powstające technologie powodują znaczące przemiany w tych obszarach.

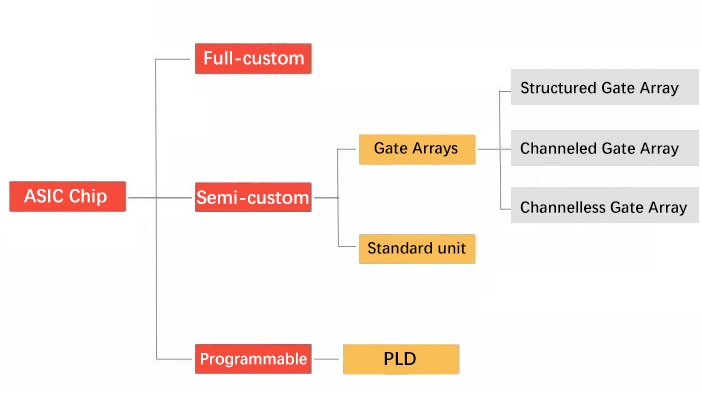

Kategoryzacja według metodologii projektowania

Metodologia projektowania urządzeń ASIC wpływa na poziom ich optymalizacji, całkowity koszt produkcji i przydatność do różnych zastosowań.

• W pełni niestandardowe żetony

W pełni niestandardowe projekty ASIC obejmują staranne wykonanie każdego tranzystora i ogniwa, aby osiągnąć najwyższą możliwą wydajność i efektywność.Ta skomplikowana metodologia jest szczególnie cenna w przypadku aplikacji wymagających niezrównanej szybkości i precyzji, takich jak procesory superkomputerowe lub systemy używane w handlu finansowym, gdzie małe opóźnienia mogą bezpośrednio wpływać na wyniki ekonomiczne.Skrupulatny charakter w pełni niestandardowego projektu zapewnia wyjątkową personalizację, ale wymaga znacznego czasu i wspólnej wiedzy w zakresie inżynierii mikroarchitektury.Zespoły pracujące nad takimi projektami często borykają się ze złożonymi wyzwaniami technicznymi związanymi z projektowaniem ręcznym.

• Pół-niestandardowe chipsy

Projekty półniestandardowe wykorzystują wstępnie przetestowane „ogniwa standardowe”, dzięki czemu inżynierowie mogą skupić się na układzie i funkcjonalności bez konieczności dostosowywania każdego pojedynczego tranzystora.Te układy ASIC są szczególnie skuteczne w sektorach takich jak systemy samochodowe lub maszyny przemysłowe, gdzie niezbędne jest połączenie niezawodności i praktycznych parametrów.Wstępnie ustrukturyzowany charakter tej metodologii skraca cykle rozwojowe, umożliwiając producentom dostosowanie harmonogramów wydawania produktów do wymagań rynku.Ta równowaga pomiędzy elastycznością i wydajnością sprzyja pragmatycznemu podejściu do rozwoju chipów, zwłaszcza gdy pojawiają się terminy lub presja skalowalności.

• Strukturalne układy ASIC (starsza macierz bramek)

Strukturalne architektury ASIC obejmują prefabrykowane tranzystory, co ogranicza dostosowywanie do połączeń wzajemnych.Chociaż ich rozpowszechnienie spadło, projekty te pozostają odpowiednie dla zastosowań niszowych, dla których priorytetem jest umiarkowana elastyczność przy obniżonych kosztach rozwoju.Na przykład niektóre starsze systemy telekomunikacyjne korzystają ze strukturalnych układów ASIC ze względu na ich przewidywalną funkcjonalność i wysoką opłacalność w dłuższym okresie życia produktu.Ich stabilność i mniejsza złożoność zapewniają wartość w kontekstach wymagających niezawodnego działania.

• Programowalne układy ASIC (FPGA/PLD)

Programowalne układy ASIC, w tym FPGA (Field Programmable Gate Arrays) i PLD (Programmable Logic Devices), są niezbędnymi komponentami na etapach prototypowania rozwoju ASIC.Ich przeprogramowalny charakter umożliwia iteracyjne testowanie i udoskonalanie, szczególnie przydatne we wczesnych projektach, w których dostosowania wydajności muszą uwzględniać dynamiczne warunki rzeczywiste.Zespoły inżynierów lotniczych często wykorzystują układy FPGA do optymalizacji algorytmów podczas lotów testowych przed sfinalizowaniem projektów ASIC.Możliwość adaptacji programowalnych urządzeń umożliwia inżynierom eksperymentowanie bez przedwczesnego przestrzegania specyfikacji produkcyjnych.

Kategoryzacja według aplikacji

Klasyfikacje oparte na aplikacjach podkreślają, w jaki sposób kluczowe branże wykorzystują architektury ASIC do spełnienia określonych wymagań technologicznych.

• TPU (jednostki przetwarzające tensor)

Jednostki przetwarzające Tensor zaprojektowano do obsługi operacji macierzowych stanowiących integralną część struktur uczenia maszynowego.Ich zdolność do wydajnego przetwarzania modeli o dużej przepustowości sprawia, że są one nieocenione w takich obszarach, jak symulacje pojazdów autonomicznych czy platformy predykcyjnej opieki zdrowotnej analizujące duże zbiory danych.Zapewniając niespotykaną dotąd prędkość obliczeniową i skalowalność, TPU na nowo definiują oczekiwania w zakresie uczenia modeli sztucznej inteligencji i złożonej analizy danych.

• LPU (jednostki przetwarzania języka)

Jednostki przetwarzania języka są zoptymalizowane pod kątem sekwencyjnego przetwarzania danych i przepustowości pamięci, co czyni je centralnymi w zadaniach związanych ze zrozumieniem języka naturalnego.Te chipy zasilają aplikacje, takie jak oprogramowanie wirtualnego asystenta umożliwiające zaawansowane zarządzanie dialogami i analizatory dokumentów oparte na sztucznej inteligencji, wykorzystywane w przepływach pracy związanych z kwestiami prawnymi lub technicznymi.LPU przodują w wypełnianiu luki pomiędzy surową mocą obliczeniową a wyrafinowanym zrozumieniem kontekstu.

• NPU (jednostki przetwarzania neuronowego)

Jednostki przetwarzania neuronowego są dostosowane do urządzeń konsumenckich wykonujących zasobooszczędne operacje AI, w tym rozpoznawanie twarzy, analizę głosu i intuicyjne sterowanie gestami.Wbudowane w smartfony, technologię noszenia i urządzenia IoT, jednostki NPU umożliwiają korzystanie z zaawansowanych funkcjonalności bez pogarszania wydajności baterii.Ich integracja odzwierciedla szersze trendy w kierunku zdecentralizowanego przetwarzania brzegowego, w którym urządzenia niezależnie wykonują złożone algorytmy, zamiast polegać na infrastrukturze chmury.

Architektury ASIC stale ewoluują wraz z nowoczesnymi wymaganiami technologicznymi.Dzięki wyspecjalizowanym projektom odpowiadającym różnym potrzebom operacyjnym inżynierowie uwalniają potencjał transformacyjny w różnych branżach.Od energooszczędnych systemów IoT po wysokowydajne szkolenia w zakresie sztucznej inteligencji, te niestandardowe konstrukcje krzemowe demonstrują trwałą wartość inżynierii precyzyjnej.Każda innowacja niesie ze sobą obietnicę zwiększonej funkcjonalności, mającej na celu sprostanie coraz bardziej złożonym wyzwaniom.

Pionierskie innowacje ASIC na nowo zdefiniują rok 2026

Innowatorzy branżowi konsekwentnie udoskonalają technologie ASIC (obwody scalone specyficzne dla aplikacji), poruszając się w szybko zmieniającym się krajobrazie, kładąc duży nacisk na utrzymanie przewagi na konkurencyjnych rynkach.Ich przełomowe osiągnięcia znacząco wpływają na takie sektory, jak przetwarzanie w chmurze, sztuczna inteligencja (AI), systemy autonomiczne i elektronika użytkowa.Poniżej szczegółowo opisano znaczące postępy.

TPU TPU v7

TPU v7 firmy Google uosabia awangardę technologii wnioskowania z modelu dużego języka (LLM) w hiperskali.Jego wyrafinowana architektura wykorzystuje szerokopasmowe połączenia optyczne wraz z pamięcią o dużej przepustowości (HBM), umożliwiając nieprzerwane przetwarzanie w czasie rzeczywistym przy jednoczesnym zachowaniu równowagi operacyjnej.Zastosowanie sieci optycznych służy zmniejszeniu opóźnień w systemach rozproszonych, co stanowi niezbędną ewolucję, aby sprostać rosnącym wymaganiom w zakresie obliczeń AI.W miarę jak aplikacje AI w dalszym ciągu zmieniają zaangażowanie człowieka i automatyzację, TPU v7 jawi się jako instrumentalny krok w kierunku niespotykanej dotąd skalowalności w rozumieniu języka naturalnego i wdrażaniu inteligentnych systemów.

Szkolenie AWS 3

Amazon Web Services (AWS) zwiększa swoją rolę w rozwiązaniach AI skoncentrowanych na chmurze dzięki wypuszczeniu Trainium 3, chipa dostosowanego do szkolenia ekspansywnych modeli sztucznej inteligencji przy zwiększonej efektywności kosztowej.Jego konstrukcja optymalizuje wzajemne oddziaływanie mocy obliczeniowej i przystępności cenowej, uwzględniając rosnącą powszechność usług sztucznej inteligencji wykorzystywanych w przemyśle na całym świecie.AWS wykorzystuje głęboką wiedzę specjalistyczną wynikającą z rozległej infrastruktury sztucznej inteligencji, wprowadzając udoskonalenia oprogramowania do Trainium 3, zapewniając zarówno dostępność, jak i wydajność, co jest kluczowym czynnikiem dla przedsiębiorstw i instytucji badawczych pragnących przyspieszyć swoje możliwości w zakresie sztucznej inteligencji.

Microsoftu Maia 100

Firma Microsoft poczyniła ogromne postępy dzięki układowi Maia 100 ASIC, innowacjom mającym kluczowe znaczenie dla zapewnienia płynnej wydajności sztucznej inteligencji na platformie Azure i systemach ChatGPT.Sercem osiągnięć Maia 100 są ulepszone przepływy danych i precyzyjnie dostrojone algorytmy, umożliwiające wydajną obsługę różnorodnych obciążeń AI, takich jak interfejsy konwersacyjne, przetwarzanie języka naturalnego i modelowanie predykcyjne.Atrybuty te odpowiadają zmieniającym się wymaganiom w zakresie natychmiastowej reakcji i rygoru obliczeniowego w najnowocześniejszych dziedzinach.

Chip Tesli Dojo

Chip Dojo Tesli wprowadza transformacyjne możliwości przetwarzania dostosowane do wizji komputerowej i systemów autonomicznych czasu rzeczywistego.Dzięki niezwykłej szybkości reakcji w analizie bodźców zmysłowych i niezrównanej wydajności sieci neuronowej, chip obsługuje zaawansowane rozwiązania w rozpoznawaniu wzorców ruchu drogowego, optymalizacji reakcji sytuacyjnych podczas jazdy nocą lub w trudnych warunkach pogodowych oraz modele adaptacyjnego podejmowania decyzji.Wyobrażając sobie na nowo rolę układów ASIC w technologii pojazdów autonomicznych, Tesla przedstawia fascynującą wizję przyszłości inteligentnego, skalowalnego transportu.

Układy ASIC zorientowane na konsumenta

W elektronice użytkowej odnotowano znaczny postęp w zakresie funkcjonalności sztucznej inteligencji na urządzeniach, możliwej dzięki chipom takim jak Neural Engine firmy Apple i Hexagon NPU firmy Qualcomm.Te układy ASIC optymalizują procesy, takie jak rozpoznawanie twarzy, asystenci głosowi i personalizacja sterowana przez użytkownika, zapewniając płynne doświadczenia użytkownika, a jednocześnie poprawiając bezpieczeństwo dzięki funkcjom sztucznej inteligencji offline.Takie postępy zmniejszają zależność od stałej łączności w chmurze, wspierając aplikacje zapewniające większą prywatność, dostosowane do indywidualnych preferencji.Ponadto wspólne wysiłki producentów urządzeń i innowatorów chipów w dalszym ciągu zmieniają oczekiwania dotyczące dostępnej sztucznej inteligencji w technologiach osobistych.

Transformacja całej branży poprzez strategiczną konkurencję ASIC

Błyskawiczny rozwój technologii ASIC podkreśla kluczową zmianę w światowych gałęziach przemysłu.W rozwijającym się „wyścigu zbrojeń AI” główni gracze rywalizują o dominację konkurencyjną w takich dziedzinach, jak ekosystemy oparte na chmurze, maszyny autonomiczne i urządzenia konsumenckie.Intensywność ta odzwierciedla zarówno krótkoterminowe ambicje, jak i dalekosiężne strategie mające na celu zrewolucjonizowanie takich obszarów, jak rzeczywistość rozszerzona, precyzyjny monitoring środowiska i pojawienie się wzajemnie połączonej infrastruktury.W miarę jak korporacje eksplorują niestandardowe projekty układów ASIC w celu znalezienia nowych nisz, implikacje wykraczają poza rentowność, stwarzając wyzwania i możliwości, które na nowo zdefiniują synergię człowieka i maszyny.

Wniosek

Układy ASIC w dalszym ciągu na nowo definiują współczesne obliczenia, zapewniając wysoką wydajność, niskie opóźnienia i efektywność energetyczną dla docelowych zastosowań.Ich siła leży w specjalizacji, co czyni je idealnymi do wnioskowania AI, obliczeń brzegowych i systemów czasu rzeczywistego, a ich ograniczenia obejmują wysokie koszty rozwoju i zmniejszoną elastyczność w porównaniu z procesorami graficznymi.Ponieważ branże wymagają szybszego i bardziej wydajnego przetwarzania, innowacje ASIC w dalszym ciągu koncentrują się na równoważeniu wydajności, skalowalności i efektywności energetycznej.W związku z ciągłym postępem w metodach projektowania i architekturze oczekuje się, że układy ASIC odegrają rolę w kształtowaniu przyszłych technologii w wielu sektorach.

Często zadawane pytania [FAQ]

1. Jakie są praktyczne zastosowania chipów ASIC?

Chipy ASIC są stosowane w systemach, które wymagają dużej szybkości i wydajności do określonego zadania.Są powszechne w przetwarzaniu sztucznej inteligencji, bezpiecznych systemach danych, urządzeniach mobilnych i elektronice samochodowej.Pomagają m.in. przyspieszyć przetwarzanie danych w AI, obsługiwać szyfrowanie w bezpiecznych systemach, usprawniać przetwarzanie sygnałów w smartfonach czy wspierać funkcje radarów w nowoczesnych pojazdach.Ich ukierunkowana konstrukcja pozwala im wykonywać te zadania szybko i przy niskim zużyciu energii.

2. Jakie są główne cechy technologii chipów ASIC?

Technologia ASIC jest znana z wysokiej specjalizacji i wydajności.Każdy chip został zaprojektowany do jednego celu, co pozwala mu działać lepiej niż zwykłe procesory w tym zadaniu.Usuwa niepotrzebne funkcje i skupia się tylko na tym, co potrzebne, co poprawia prędkość i zmniejsza zużycie energii.To sprawia, że układy ASIC są idealne do zastosowań wymagających stabilnej, spójnej i zoptymalizowanej wydajności.

3. Jak chipy ASIC wykonują swoje zadania?

Chipy ASIC działają w oparciu o stałe obwody projektowane podczas produkcji.Po zbudowaniu spełniają ustaloną funkcję i nie można ich zmienić.Ta stała konstrukcja pozwala im bardzo efektywnie wykonywać swoje zadania, takie jak przetwarzanie danych AI lub uruchamianie algorytmów szyfrowania.Ponieważ nie są elastyczne jak inne procesory, skupiają się na bardzo dobrym wykonywaniu jednego zadania przy dużej prędkości i niskim zużyciu energii.

Powiązany blog

-

Ile zer na milion, miliard, bilion?

2024/07/29

Million reprezentuje 106, łatwo chwytana liczba w porównaniu do przedmiotów codziennych lub rocznych pensji. Miliard, równoważny 109, zaczyna roz... -

IRLZ44N MOSFET Arkusz, obwód, równoważny, pinout

2024/08/28

IRLZ44N to szeroko stosowany Mosfet Power N-Kannel.Znany z doskonałych możliwości przełączania, jest bardzo odpowiedni do wielu zastosowań, szcz... -

Temperatura akumulatora zbyt niska, ładowanie zatrzymało się.Jak to naprawić?

2024/10/6

Problemy z ładowaniem baterii telefonu komórkowego są powszechne, ale można je skutecznie zarządzać.Temperatura odgrywa dużą rolę w wydajnoś... -

BC547 Tranzystor Kompleksowy przewodnik

2024/07/4

Tranzystor BC547 jest powszechnie stosowany w różnych zastosowaniach elektronicznych, od podstawowych wzmacniaczy sygnałowych po złożone obwody o... -

Kompleksowy przewodnik po SCR (prostownik kontrolowany krzem)

2024/04/22

Kontroli prostownicy (SCR) lub Thyristors odgrywają kluczową rolę w technologii elektroniki energetycznej ze względu na ich wydajność i niezawod... -

Podstawy obwodów OP-AMP

2023/12/28

W skomplikowanym świecie elektroniki podróż do jej tajemnic niezmiennie prowadzi nas do kalejdoskopu komponentów obwodów, zarówno wykwintnych, j... -

LR621, SR621SW, 364, AG1 Equivivalents i zamienniki

2024/07/15

Baterie przycisków LR621 i SR621SW są powszechne w kompaktowych urządzeniach elektronicznych, takich jak zegarki, małe zabawki, kalkulatory i zdal... -

Porównanie różnic i zastosowań NMOS i PMOS

2024/11/15

Zrozumienie różnic między tranzystorami NMOS i PMO jest ważne w projektowaniu wydajnych obwodów.NMOS (NMOS-semiconductor) i PMOS (typ p-tlenku-tl... -

Co oznaczają STD, AGM i GEL na ładowarce

2024/07/10

Tradycyjne ładowarki akumulatorów ołowiowych są znane ze swojej prostoty i niezawodności.Od lat skutecznie służą swoim celu, głównie ze wzgl... -

Kompletny przewodnik po multiplekserach i ich rola w systemach cyfrowych

2025/09/20

Multipleksery są komponentami w systemach cyfrowych, zaprojektowanych do kierowania wieloma sygnałami wejściowymi do pojedynczej linii wyjściowej ...

Gorące części

- C1005C0G2A681K050BC

- AD587JQ

- UCB1400BEVM

- AM29DL320GB-70EI

- MC10105FN

- C2012CH2E222K125AA

- MT48LC32M16A2P-75IT

- 06031C822JAT2A

- ERA-3AEB1132V

- TPS54060DRCT

- SST39WF400A-90-4C-VA

- MAX3261CCJ

- 1812HC392KAZ1A

- MAX1791EUB+T

- GRM2166S1H221JZ01D

- C1005C0G1H680J050BA

- ES29LV320EB-70TGI

- ADR392BUJZ

- S71NS128NAOBJWSE3

- TN0200T-T1

- MC908QY8CDWE

- 0402YC332JAT2A

- RT1206DRD0727RL

- N25Q128A11E1240E

- AT8356264-IL3T

- UB6225PQFA1-125

- RT1206DRD07143RL

- MKA-10110

- FF600R12ME4C_B11

- XC6SLX100T-2CSG484C

- RC0603FR-0753K6L

- MAX1999EEI+T

- H27U8G8T2BTR-BC

- GRM1557U1HR40CZ01D

- C1608C0G2A271K080AA

- VI-260-23

- MIC3975-3.3YMM

- XR3070XED-F

- VSC8489YJU-02

- T491X107M020AH

- TPS22810DRVT

- L9779WD-SPI-TR

- PF38F5060M0Y0BE

- SiI13114CTU

- SST39SF010-90-4I-NH

- TEC7033-MMI

- HD4051BFP

- ST40RA166XH6E

- UPD789176GB-555-8E

- BCM56149A1KFEBG