# Tsi301™ HyperTransport to PCI User Manual

80D3000\_MA001\_02

September 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

Printed in U.S.A.

©2009 Integrated Device Technology, Inc.

## GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

# **About This Manual**

## **Notes**

This reference manual contains technical specifications for the Tsi301 HyperTransport PCI bridge chip. The manual is intended for use by system designers and developers who are using the chipset in their designs.

# HyperTransport<sup>™</sup> and LDT

In this manual, HyperTransport<sup>TM</sup> technology and LDT (Lightning Data Transport) are sometimes used interchangeably. HyperTransport<sup>TM</sup> technology and LDT both refer to identical technology based on the same specification.

Throughout the remainder of this manual HyperTransport<sup>™</sup> technology is referred to as HyperTransport.

#### Silicon Revisions: Pass1 and Pass2

Silicon revisions are referred to as Pass1 and Pass 2 throughout this document. Pass1 refers to silicon revisions 1.0 and 1.1. Pass2 refers to silicon revisions 2.0 and higher. Any information not flagged as specific to Pass1 or Pass 2 is applicable to all Tsi301 bridges. *Pass1* and *Pass2* are italicized throughout this document's text to help identify the relevant information.

The following sections describe the intended audience, scope, and the organization of this reference manual.

#### **Audience**

This reference manual is intended for system designers and others who design using the HyperTransport PCI bridge, or who evaluate computer systems based on this chip.

#### Scope

This manual describes the features, requirements, and configurations for the HyperTransport PCI bridge, including functional and physical details.

Specific details on industry standards (for example, PCI or ISA bus specifications) are not included. Additional information is available in the appropriate vendor and IEEE specifications.

#### **Conventions and Definitions**

This section describes stylistic conventions used in this manual, and defines product-specific terminology, acronyms, and other technical language used throughout this manual.

# **Information Flags**

**Note:** Notes highlight information that provides additional clarification or will ease tasks related to the assembly and operation of the system.

# **Typographic Conventions**

This manual uses the following type conventions:

- Italic type is used for document citations and information that provides supplemental clarification.

Pass1 and Pass2 are italicized throughout this document's text to help identify the relevant information.

- Courier font is used for type that appears on a screen, such as an example of computer output.

## **Signals and Bits**

- Active-Low Signals—Signal names ending in \_N, such as SFILL\_N, indicate active-low signals.

Active-low signals are asserted in their low-voltage state and negated in their high-voltage state.

- · Active-High Signals are asserted in their high-voltage state and negated in their low-voltage state.

- Differential Signals—Differential signals are indicated by the \_H and \_L suffixes. Signals ending in \_H

are the active-high half of a differential pair whereas signals ending in \_L are the active-low half of a

differential pair.

- Signal Ranges—The highest and lowest signal numbers in a range of signals are contained in brackets and separated by a colon; for example D[63:0].

- Reserved Bits and Signals—Signals or bus bits marked reserved must be driven inactive or left

unconnected, as indicated in the signal descriptions. These bits and signals are reserved by API

NetWorks, Inc. for future implementations. When software reads registers with reserved bits, the

reserved bits must be masked. When software writes such registers, it must first read the register and

change only the non-reserved bits before writing back to the register.

#### **Data**

The following list defines data terminology:

- Quantities

- A word (W) is two bytes (16 bits).

- A doubleword (DW) is four bytes (32 bits).

- A quadword (QW) is eight bytes (64 bits).

- Abbreviations—The following notation is used for bits and bytes:

- Kilo—K, as in 4-Kbyte page (2<sup>10</sup>).

- Mega—M, as in 4 Mbits/sec (2<sup>20</sup>).

- Giga—G, as in 4 Gbytes of memory space (2<sup>30</sup>).

- Little-Endian Convention—The byte with the address xx...xx00 is in the least-significant byte position (little end). In byte diagrams, bit positions are numbered from right to left: The little end is on the right, and the big end is on the left.

- Bit Ranges—In text, bit ranges are shown with a colon (for example, 3:0). When accompanied by a signal or bus name, the highest and lowest bit numbers are contained in brackets and separated by a colon (for example, AD[31:0]).

- Bit Values—Bits can either be set to 1 or cleared/reset to 0.

- Hexadecimal and Binary Numbers—Unless the context makes interpretation clear, hexadecimal numbers are followed by an h, binary numbers are followed by a b, and decimal numbers are followed by a d.

#### **Acronvms**

The following is a list of acronyms used in this document.

| Acronym | Definition                                 |

|---------|--------------------------------------------|

| APIC    | Advanced Programmable Interrupt Controller |

| BIOS    | Basic Input/Output System                  |

| CSR     | Control/Status Register                    |

| DAC     | Dual Address Cycle                         |

| DDR     | Double Data Rate                           |

| DMA     | Direct Memory Access                       |

| DRAM    | Direct Random Access Memory                |

| ESBGA   | Enhanced Super Ball Grid Array             |

| FIFO    | First In, First Out                        |

| HSTL    | High-Speed Transistor Logic                |

| I/O     | Input/Output                               |

| Acronym | Definition                              |

|---------|-----------------------------------------|

| ISA     | Industry Standard Architecture          |

| LSB     | Least Significant Bit                   |

| LVD     | Low Voltage Differential                |

| LVTTL   | Low Voltage Transistor-Transistor Logic |

| MRL     | Memory Read Line                        |

| MRM     | Memory Read Multiple                    |

| MSB     | Most Significant Bit                    |

| MWI     | Memory Write Invalid                    |

| NDA     | Non-disclosure Agreement                |

| NMI     | Non-maskable Interrupt                  |

| ORC     | Outbound Request Controller             |

| OS      | Operating System                        |

| PBGA    | Plastic Ball Grid Array                 |

| PCB     | Printed Circuit Board                   |

| PIO     | Programmed Input/Output                 |

| PCI     | Peripheral Component Interconnect       |

| PLL     | Phase Locked Loop                       |

| SBGA    | Super Ball Grid Array                   |

| SDRAM   | Synchronous Direct Random Access Memory |

| SE      | Single-ended                            |

| SIP     | Serial Initialization Packet            |

| SPD     | Serial Presence Detect                  |

| SRI     | Serial ROM Interface                    |

| SROM    | Serial Read Only Memory                 |

| SRAM    | Static Random Access Memory             |

| SRM     | System Reference Manual                 |

| NI - 4                      |                  |

|-----------------------------|------------------|

| Notes                       |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             |                  |

|                             | L                |

| Tsi301 HyperTransport to PC | Cl User Manual 6 |

# **Chapter 1 Bridge Features**

# **Notes**

This chapter describes the features and operation of the API NetWorks HyperTransport PCI bridge.

# 1.1 HyperTransport PCI Bridge Features

The HyperTransport PCI bridge is an I/O bridge from HyperTransport to PCI with the following features:

- An 8-bit HyperTransport primary interface capable of running at data rates up to 800 Mb/s and compliant with Lightning Data Transport I/O Link Protocol Specification, Revision 1.0.

- A 64-bit, 66 MHz PCI secondary interface compliant with the PCI Local Bus Specification, Revision 2.2.

- A PCI arbiter supporting six external bus masters (not counting the Tsi301) and compliant with the PCI Local Bus Specification, Revision 2.2.

- A HyperTransport interrupt controller with configurable support for up to 20 interrupt sources in Pass1, and 16 interrupt sources in Pass2.

- A configuration register set and programming model consistent with the *PCI-to-PCI Bridge* Architecture Specification, Revision 1.1.

- Power-up configuration through Serial Initialization Packet (SIP) or pin sampling.

# 1.2 HyperTransport Interface

The HyperTransport PCI bridge primary interface is a HyperTransport tunnel. The primary interface is compliant with *Lightning Data Transport I/O Link Protocol Specification, Revision 1.0* with the exception that the Tsi301 does not support 2 and 4 bit HyperTransport interfaces and does not support Dynamic Frequency Programming. The interface contains two HyperTransport links which allow the connection of multiple bridge chips in a daisy-chain configuration.

Each HyperTransport link has an 8-bit DDR transmit and an 8-bit DDR receive port running at clock speeds up to 400 MHz, allowing for raw bandwidth of 800 MB/s simultaneously in each direction. With protocol overhead, the maximum sustainable bandwidth in one direction is approximately 705 MB/s.

- For testing, or connection to slower devices, the HyperTransport PCI bridge may be programmed to operate at slower link clock rates.

- The HyperTransport PCI bridge supports both the synchronous and asynchronous modes of link initialization.

## 1.3 PCI Interface

The HyperTransport PCI bridge secondary interface is a 64-bit, 66 MHz capable PCI bus. The HyperTransport PCI bridge supports running the bus in 32-bit mode at either 33 MHz or 66 MHz. A lower performance mode is also supported in which the PCI bus runs at 25 or 50 MHz. The bus can be configured for compatibility with 3.3 V or 5.0 V operation, although 50 and 66 MHz are only supported at 3.3 V.

The HyperTransport PCI bridge supports the full 40-bit memory-mapped space and 25-bit I/O space described in the *Lightning Data Transport I/O Link Protocol Specification, Revision 1.0.* In *Pass1*, PCI addresses outside these spaces alias into them. In *Pass2*, PCI addresses outside these spaces are left on the PCI bus. PCI dual address cycle (DAC) support is provided both inbound and outbound to support the memory-mapped space.

- The HyperTransport PCI bridge supports configuration accesses to devices 0–15, using Address/Data (AD) bits 16–31 for IDSEL#.

- The HyperTransport PCI bridge implements all parity and error-checking features described in the PCI Local Bus Specification, Revision 2.2.

#### 1.3.1 PCI Master

As a PCI master, the HyperTransport PCI bridge chip can generate MemRd/Wr, IORd/Wr, and ConfigRd/Wr cycles.

- The HyperTransport PCI bridge does not implement a cacheline size register and does not prefetch to PCI, so it never generates MemRdLine, MemRdMult, or MemWrlnv cycles.

- The HyperTransport PCI bridge does not support a Southbridge connection to its PCI bus, so it never generates INTA cycles.

- The HyperTransport PCI bridge does not generate Special cycles.

PCI master cycles that are retried or disconnected on the PCI bus are reissued locally by the HyperTransport PCI bridge until they complete. The HyperTransport PCI bridge can track up to four outstanding requests in the Outbound Request Controller, of which a maximum of three may be nonposted requests. The HyperTransport PCI bridge rotates among these requests to maximize bandwidth in the presence of retries or disconnects.

#### 1.3.2 PCI Slave

As a PCI slave, the HyperTransport PCI bridge can respond to all types of memory and I/O cycles. However, the HyperTransport PCI bridge never responds to PCI configuration cycles.

- The HyperTransport PCI bridge employs medium DEVSEL# timing.

- All PCI slave writes, including I/O writes, are posted.

- A total of 48 doublewords (DW) of write data buffering are provided on the chip.

- All PCI slave reads are implemented as delayed requests, with up to four delayed requests outstanding at once.

Prefetching is supported for all flavors of memory read cycle, with separate prefetch controls for each cycle type and a maximum prefetch per read of 128 DW. Prefetching may be done once at the beginning of each read, or it may be enabled to continuously issue requests as data is drained to PCI. All prefetch data is discarded when the read disconnects on the PCI bus. The bridge chip provides buffer space for a total of 256 DW of read prefetch data.

#### 1.3.3 PCI Arbiter

The HyperTransport PCI bridge implements an on-chip two-level PCI Arbiter with request/grant pairs: 7 pairs in *Pass1*, 6 pairs in *Pass2*. The request/grant pairs in *Pass1* include two high-priority sets for the on-chip PCI master, one high priority set for an external requester, and five symmetrical sets for external device use. In *Pass2*, there is one high-priority set for the on-chip PCI master.

All connections to the arbiter are through external pins, so its use is optional. The HyperTransport PCI bridge chip may also be configured to use an external PCI arbiter.

# 1.4 Interrupt Controller

The HyperTransport PCI bridge implements a HyperTransport interrupt controller. In *Pass1*, there are 20 external interrupt sources. In *Pass2*, there are 16 external interrupt sources.

The interrupts pins may be programmed in groups of four to be level or edge-triggered and active high or low. In *Pass1*, one group can also be used to generate the special PC compatibility interrupts: SMI, NMI, INIT, and INTR. In *Pass2*, SMI, NMI, INIT, and INTR are not available.

# 1.5 Configuration

Most HyperTransport PCI bridge configuration is done under host software control through accesses across HyperTransport to the bridge chip's control/status register (CSR) set. However, some hardware initialization is required to bring up the HyperTransport links before software configuration can occur. To support hardware initialization, the HyperTransport PCI bridge provides a Serial Initialization Packet (SIP) interface to read an external SROM during a cold reset sequence.

To reduce external part count, a small number of configurations are pre-programmed into the HyperTransport PCI bridge. These pre-programmed configurations may be selected using PCI bus pins during cold reset in the absence of an SROM.

# 1.6 Interface Levels

A complete pinout of the HyperTransport PCI bridge is given in the Signals Chapter. The rough grouping of signal types is shown in Table 1.

| Interface      | Group          | Voltages                                           |  |

|----------------|----------------|----------------------------------------------------|--|

| PCI            | PCI            | 3.3V, 5.0V tolerant                                |  |

| HyperTransport | HyperTransport | Differential, 600 mV swing, centered on 600 mV     |  |

| Interrupts     | INT            | In <i>Pass1</i> , 2.5 V<br>In <i>Pass2</i> , 3.3 V |  |

Table 1 HyperTransport PCI Bridge Interface Voltages

# 1.7 Clocking

In normal operation, the HyperTransport PCI bridge's reference clock (REFCLK\_H/L) comes from a PCI bus clock. This clock is received from the same source that drives clocks to devices on the bridge's PCI bus and is nominally in phase with it; although it may be delayed relative to the other PCI bus clocks. Reference clock frequency is indicated by the P\_M66EN pin. From this input, an internal phase locked loop (PLL) generates the HyperTransport PCI bridge internal core clock and the HyperTransport transmit clocks.

**Note:** In Pass1, the reference clock frequency and P\_M66EN can be set at either 33 or 66 MHz at L\_PWROK and must remain static. In Pass2, clocks and P\_M66EN can be used in the same way; or the PCI bus frequency can be changed without resetting the HyperTransport PCI bridge. To support changing the PCI bus frequency without resetting the HyperTransport PCI bridge, REFCLK\_H/L must always run at 33 MHz and P\_M66EN must indicate 33 MHz at the rising edge of L\_PWROK. The clock frequency to the PCI devices and P\_M66EN can then be switched between 33 and 66 MHz whenever AP\_RST is asserted. The clocks must still be nominally in phase and rising edges of the reference clock must be aligned with rising edges of the PCI bus clock.

If the HyperTransport PCI bridge is to perform synchronous link initialization with the HyperTransport devices on either side of it, the reference clock must be derived from the same base frequency source. If not, asynchronous link initialization must be used. No phase relationship is required in either mode.

For debug and test purposes, the HyperTransport PCI bridge allows bypassing of the PLL. It provides separate bypass clock inputs for the core and HyperTransport transmit clocks. The bypass clocks run directly at the frequency provided. Both bypass clocks must be derived from the same base frequency source.

| Notes                       |                     |

|-----------------------------|---------------------|

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

|                             |                     |

| Tsi301 HyperTransport to PC | Cl User Manual 1-10 |

# **Chapter 2 Signal Descriptions**

# **Notes**

# 2.1 HyperTransport Signals

**Note:** The Lx\_ prefix denotes signals associated with either HyperTransport Link 0 (x=0) or HyperTransport Link 1 (x=1).

The PCI bridge HyperTransport implementation is a standard HyperTransport design. Table 2.1 lists all HyperTransport signals. For details on the characteristics of these signals, refer to the *Lightning Data Transport I/O Link Protocol Specification, Revision 1.0* and the *Lightning Data Transport Electrical Specification, Revision 0.77*, both from AMD.

| Signal Name        | I/O Type | Signal Type     |

|--------------------|----------|-----------------|

| Lx_RX_CLK_H/L      | Input    | HyperTransport  |

| Lx_RX_CTL_H/L      | Input    | HyperTransport  |

| Lx_RX_CAD[7:0]_H/L | Input    | HyperTransport  |

| Lx_TX_CLK_H/L      | Output   | HyperTransport  |

| Lx_TX_CTL_H/L      | Output   | HyperTransport  |

| Lx_TX_CAD[7:0]_H/L | Output   | HyperTransport  |

| Lx_VLDT[2:0]       | Power    | 1.2 volt        |

| L_TSTRST_N         | Input    | 2.5 volt LVCMOS |

| L_POWER_OK         | Input    | 2.5 volt LVCMOS |

| L_RST_N            | Input    | 2.5 volt LVCMOS |

Table 2.1 HyperTransport Bridge Signals

# 2.2 PCI Signals

The HyperTransport PCI bridge implements a standard PCI interface, as detailed in *PCI Local Bus Specification, Revision 2.2*. Table 2.2 lists all HyperTransport PCI bridge PCI signals.

| Signal<br>Name | I/O Type      | Signal Type |

|----------------|---------------|-------------|

| P_CBE_N[7:0]   | Bidirectional | PCI         |

| P_AD[63:0]     | Bidirectional | PCI         |

| P_PAR          | Bidirectional | PCI         |

| P_SERR_N       | Input         | PCI         |

| P_PERR_N       | Bidirectional | PCI         |

| P_LOCK_N       | Bidirectional | PCI         |

| P_STOP_N       | Bidirectional | PCI         |

| P_DEVSEL_N     | Bidirectional | PCI         |

| P_TRDY_N       | Bidirectional | PCI         |

Table 2.2 HyperTransport Bridge PCI Signals

| Signal<br>Name | I/O Type                        | Signal Type |  |

|----------------|---------------------------------|-------------|--|

| P_IRDY_N       | Bidirectional                   | PCI         |  |

| P_FRAME_N      | Bidirectional                   | PCI         |  |

| P_REQ64_N      | Bidirectional PCI               |             |  |

| P_ACK64_N      | Bidirectional                   | PCI         |  |

| P_PAR64        | Bidirectional                   | PCI         |  |

| AP_RST_N       | Pass1 Output Pass2 Input/Output | Open Drain  |  |

| P_M66EN        | Input                           | PCI         |  |

| P_WSC_N        | Reserved                        | PCI         |  |

Table 2.2 HyperTransport Bridge PCI Signals<Emphasis> (Continued)

Table 2.3 lists the PCI Arbitration signals, which are not defined by the PCI specification.

| Signal Name  | I/O Type | Signal Type |

|--------------|----------|-------------|

| P_REQ_OUT_N  | Output   | PCI         |

| P_GNT_IN_N   | Input    | PCI         |

| P_REQ[5:0]_N | Input    | PCI         |

| P_GNT[5:0]_N | Output   | PCI         |

| P_PREQ_N     | Input    | PCI         |

| P_PGNT_N     | Output   | PCI         |

**Table 2.3 PCI Arbitration Signals**

**Note:** Any unused P\_REQ[5:0]\_N or P\_PREQ\_N requests should be pulled to 3.3 volts (inactive).

# 2.2.1 PCI Signal Levels

The HyperTransport bridge supports PCI 3.3 V levels and PCI 5.0 V levels as determined by AP\_TYPEDET\_N and VDD3050\_PCI[7:0]. AP\_TYPEDET\_N is related to PCI functionality but not part of the PCI specification.

If AP\_TYPEDET\_N is pulled low and VDD3050\_PCI[7:0] is at 3.3 V, PCI signals conform to the PCI 3.3 V signalling rules.

If AP\_TYPEDET\_N is pulled high and VDD3050 PCI[7:0] is at 5.0 V, PCI signals conform to the PCI 5.0 V signalling rules.

No other combinations of AP\_TYPEDET\_N and VDD3050 PCI[7:0] are supported.

# 2.3 Interrupt and Error Signals

**Note:** In Pass2, SMI, NMI, INIT, and INTR are not available. Customers should use the BLKx\_INT[y] signals instead.

## BLKx\_IRQ[y]

Functionally input only. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

Generic interrupt input signals. The HyperTransport PCI bridge has four blocks of generic interrupts, with four interrupts per block. The lower 2 bits of the vector are contained in each interrupt. The upper 6 bits are in the interrupt block description register.

The y denotes four separate signals associated with each of the four interrupt blocks x, for a total of 16 signals.

Note: In Pass1 if this pin is not needed for an interrupt, it can be floated or pulled to 2.5 volts.

In Pass2 if this pin is not needed for an interrupt, it can be floated or pulled to 3.3 or 2.5 volts. 3.3 volts is preferable.

# **NMI**

Bidirectional. In Pass1, 2.5 volt LVCMOS. In Pass2, this signal is absent.

Non-Maskable Interrupt Signal. This signal is not available in Pass2. Customers should use the BLKx\_INT[y] signals instead.

Note: In Pass1 if this pin is not needed for an interrupt, it can be floated or pulled to 2.5 volts.

# SMI\_N

Bidirectional. In Pass1, 2.5 volt LVCMOS. In Pass2, this signal is absent.

System Management Interrupt Signal. This signal is not available in Pass2. Customers should use the BLKx\_INT[y] signals instead.

Note: In Pass1 if this pin is not needed for an interrupt, it can be floated or pulled to 2.5 volts.

## INTR

Input. In Pass1, 2.5 volt LVCMOS. In Pass2, this signal is absent.

Interrupt Input Signal. This signal is not available in Pass2. Customers should use the BLKx\_INT[y] signals instead.

## INIT

Bidirectional. In Pass1, 2.5 volt LVCMOS. In Pass2, this signal is absent.

x86 INIT signal. This signal is not available in Pass2. Customers should use the BLKx\_INT[y] signals instead.

**Note:** In Pass1 if this pin is not needed for an interrupt, it can be floated or pulled to 2.5 volts.

# FATAL\_ERR\_N

Open Drain Output. In Pass1, 2.5 volt open drain LVCMOS. In Pass2, 3.3 volt open drain LVCMOS.

The HyperTransport PCI bridge has detected a fatal error.

#### **NONFATAL ERR N**

Open Drain Output. In Pass1, 2.5 volt open drain LVCMOS. In Pass2, 3.3 volt open drain LVCMOS.

The HyperTransport PCI bridge has detected a non-fatal error.

# 2.4 SIP Signals

#### **SROM SCK**

Bidirectional. In Pass1, 2.5 volt open drain LVCMOS. In Pass2, 3.3 volt open drain LVCMOS.

P\_AD[1] drives the CLK pin of the SIP ROM. During reset, if this pin is pulled high with a 10 K resistor, the SROM supplies the entire SIP packet. If low, the SIP packet is generated internally.

## SROM\_SDA

Bidirectional. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

This pin is the data pin of the SIP ROM.

# 2.5 Test Signals

For systems using Pass1 of the HyperTransport PCI bridge, the TDI and TDO pins are not guaranteed to be quiescent during scan operations. Customers should ensure their JTAG implementation on the PCB is tolerant of this.

#### **TCK**

Input. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

In *Pass1*, this is a reserved input and can be left floating or pulled to GND.

In Pass2, this is the JTAG clock input.

#### TDI

Pass1 output. Pass2 input. In Pass1, 2.5 volt open drain LVCMOS. In Pass2, 3.3 volt open drain LVCMOS.

In Pass1, this is a reserved output and not guaranteed to be quiet.

In Pass2, this is the JTAG data input.

## **TDO**

Output. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

In Pass1, this is a reserved output and not guaranteed to be quiet.

In Pass2, this is the JTAG data output.

#### **TMS**

Input. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

In Pass1, this is a reserved input and can be left floating or pulled to GND.

In Pass2, this is the JTAG mode select.

#### TRST N

Input. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

In Pass1, this is a reserved input.

In Pass2, this is the JTAG reset input.

**Note:** This signal should be pulled low for normal functional mode.

# **TMODE [3:0]**

Input. Test pins. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

#### TRISTATE\_N

Input. In Pass1, 2.5 volt LVCMOS. In Pass2, 3.3 volt LVCMOS.

Tristate enable, see the Signals Chapter.

#### **VBB**

This pin is tied to the substrate for testing purposes. It should not be connected on the PCB. This signal is not available in *Pass2*.

# 2.6 PLL/Clock Signals

# REFCLK\_H/L

Input. GTL+.

This 33/66 MHz input is the reference for the HyperTransport PCI bridge PLL. To improve 66 MHz timing, it may be delayed relative to other PCI clocks on the PCI bus. This is a differential signal. The \_L input can be attached to the active-low half of a differential pair, or it can be tied to a reference voltage.

## REFCLK\_PLL\_BYPASS

Input. 2.5 volt LVCMOS.

When this signal is asserted, the PLL is bypassed. REFCLK\_H/L input pins are used directly to drive internal clocks.

# REFCLK\_PLL\_VCC

This is the 2.5 V power input for the PLL.

#### **REFCLK PLL GND**

This is the ground input for the PLL.

# 2.7 Core and I/O Power Signals

#### **VDD**

Core power. 2.5 V.

#### **VSS**

Ground.

#### **VDDQ\_AP[18:0]**

PCI VDD supply voltage. Always 3.3 V, regardless of whether the HyperTransport bridge is using 3.3 V PCI levels or 5.0 V PCI levels.

## VDD3050\_PCI[7:0]

If AP\_TYPEDET\_N is pulled low, these should be at 3.3 V. PCI signalling will conform to the 3.3 V rules.

If AP\_TYPEDET\_N is pulled high, these should be at 5.0 V. PCI signalling will conform to the 5.0 V rules.

# VDD3P\_AGP[3:1]

In Pass1, 3.3 V.

In Pass2, these signals are absent.

#### Lx\_VLDT[y]

HyperTransport I/O power. 1.2 V.

# 2.8 Calibrator Logic Signals

# Lx\_RREF\_GND/Lx\_RREF

# **Bidirectional**

These signals are used by the HyperTransport calibrator logic. A resistor should be placed between these two pins. The resistor value should be equal to half of the differential impedance of the HyperTransport signals, which is 100 ohms +/- 10%.

**Note:** The LDT\_RREF\_GND should not be connected to ground.

# **Chapter 3 Functional Operation**

# **Notes**

This chapter details the operation of the HyperTransport PCI Bridge chip.

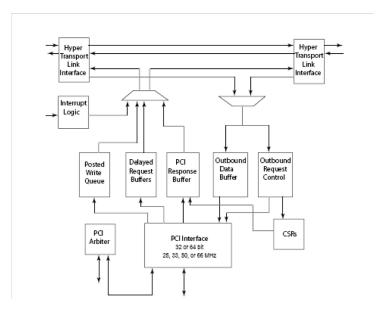

Figure 3.1 HyperTransport PCI Bridge Block Diagram

# 3.1 HyperTransport Interface

The HyperTransport PCI bridge HyperTransport interface consists of two identical link interfaces, each with a HyperTransport transmitter and receiver. Some central reset and error-handling logic is shared between the two links.

In the HyperTransport protocol, all logical packet transfer is between HyperTransport slaves and the host. Direct peer-to-peer communication is not allowed. To support peer-to-peer operations, packets are reflected through the host. Packets issued from the host to a HyperTransport slave are defined to travel downstream on the HyperTransport chain. Packets issued from a HyperTransport slave to the host are defined to travel upstream. Intermediate nodes in the daisy chain forward packets from link to link until they reach their final destination, which accepts the packet.

Link interfaces in the HyperTransport PCI bridge are symmetrical, which allows connection of either bridge link toward a host. The HyperTransport PCI bridge also supports being placed in a double-hosted chain with hosts at both ends.

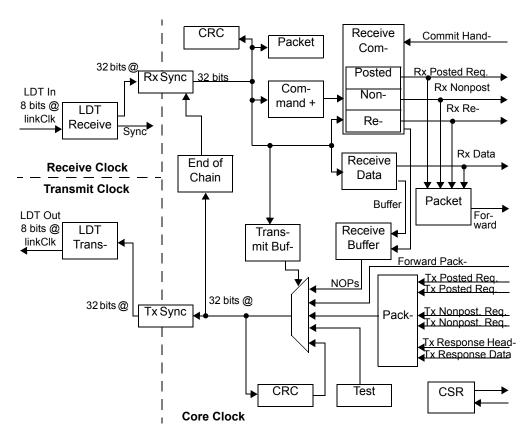

Figure 3.2 shows a block diagram of a single HyperTransport link interface.

Figure 3.2 Single HyperTransport Link Interface Block Diagram

# 3.2 HyperTransport Packet Reception

Packets received from HyperTransport are placed into the HyperTransport Receive (Rx) buffers. The HyperTransport flow control algorithm guarantees that no packet is received without buffer space to store it. Packet contents are divided into command information (including address) and data, with separate buffers for each.

- Command buffers are statically partitioned among the three virtual channels (posted requests, non-posted requests, and responses), with each channel allocated space to hold four commands.

- Data buffers are shared among the three virtual channels and dynamically allocated among them.

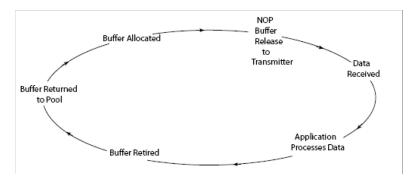

A total of eight data buffers are provided. Allocation of buffers to virtual channels is controlled by the Data Buffer Allocation CSR (6Dh:6Ch). As data buffers are allocated, buffers are released from the pool to each channel. As the buffers are retired, they return to the pool.

## 3.2.1 Data Buffer Allocation

Each virtual channel always needs at least one data buffer allocated to it to prevent deadlock. A data buffer is considered allocated to a virtual channel if it has been released to that channel and is awaiting data, or if it has received data but has not yet been retired. Two types of user specified data buffer allocation are allowed:

- Guaranteed buffers specified in the NeedPReq, NeedNpReq, and NeedResp CSR fields.

- Assigned but not guaranteed buffers specified in the WantPReq, WantNpReq, and WantResp CSR fields.

Guaranteed data buffer allocations to each channel are user configurable using NeedPReq, NeedNpReq, and NeedResp CSR fields to set minimum buffer allocations for each virtual channel. If retiring a data buffer to the pool would cause a virtual channel to fall below its allocation, that buffer is immediately re-allocated to the

same channel. Re-allocation guarantees that the minimum allocation set in the Need CSR fields will always be met as long as the sum of the CSR values is less than or equal to the total number of data buffers in the link interface.

The buffer allocation strategy is to always keep some number of granted but unfilled buffers allocated to each virtual channel so that data is always able to move. Once the minimum configured allocations are met, remaining unallocated buffers are brought out of the pool and granted based on traffic demands. These are the assigned buffers specified in WantPReq, WantNpReq, and WantResp.

The WantPReq, WantNpReq, and WantResp CSR fields specify the number of free buffers attempted (not guaranteed) for each channel. Whenever the number of free buffers in a particular channel drops below its Want value, a new buffer is allocated to that channel from the pool based on buffer availability. Depending on the number of full data buffers, it may not be possible to always satisfy Want buffer assignments.

The WantPReq, WantNpReq, and WantResp CSR fields allow the user to assign free buffers to the traffic most important to latency and performance. The goal is to set the Want values high enough for channels that require maximum bandwidth so that there are enough buffers available to hide the latency of a buffer release issued back to the transmitter when the first beat of a data packet is received. The pitfall is setting a channel's Want values so high that it prevents buffers from being available to the other channels, inadvertently throttling performance.

Figure 3.3 Data Buffer Life Cycle

#### 3.2.2 Packet Decode

As packets are placed in the Rx buffers, the associated commands and addresses are decoded to determine whether the HyperTransport PCI bridge is the packet target on the HyperTransport chain. These packets are also checked for ordering collisions against other packets resident in the buffers. The decode and collision results are stored in the buffers with the packets.

- Packets received on the HyperTransport interface may be routed to internal logic, including the PCI interface. This is "accepting" a packet.

- Packets may also be routed to the other HyperTransport link interface for transmission to the next device in the chain. This is "forwarding" a packet.

- A particular packet may be accepted, forwarded, or both.

The HyperTransport PCI bridge HyperTransport packet decode first determines whether the incoming packet is travelling upstream or downstream. This determination is based on the packet source information contained in the packet itself, not on which link is the upstream or downstream link.

- Upstream packets are always forwarded toward the host and are never accepted by the HyperTransport PCI chip.

- Downstream RdSized and WrSized request packet addresses are decoded according to the HyperTransport Address Map described in Section 3.3 and are accepted if they match any HyperTransport PCI bridge address ranges.

- Downstream WrSized and RdSized that do not match any of the HyperTransport PCI bridge address ranges are forwarded to the next device in the chain.

- Broadcast request addresses are also decoded and accepted if they match a HyperTransport PCI

- bridge address range. However, these packets are also always forwarded.

- Fence and Flush requests are never accepted by the HyperTransport PCI bridge and are always forwarded.

- Downstream response packets are accepted if their unitId field matches the value in the BaseUnitId field of the HyperTransport PCI bridge LdtCmd register; otherwise, they are forwarded.

## 3.2.3 Collision Checking

Collision checking is performed according to the HyperTransport protocol to determine if incoming packets are required to stay ordered behind packets already in the Rx buffers. Only packets headed to the same accept or forward destination may have ordering requirements. If a packet has an ordering collision, it may not be issued from the Rx buffers until the packet with which it collided has both been issued and reached an appropriate commit point to guarantee ordering. This ordering point varies by destination.

Because the Outbound Request Controller (ORC) can reorder requests, requests accepted by the Hyper-Transport PCI bridge may not be committed until they are retired by the ORC. For accesses to PCI, this means that the request reached the PCI bus and all data was transferred. Packets forwarded from one link to the other are streamed - meaning that transmission may start before the whole packet is received. It is the transmitter's responsibility to ensure that required packet ordering is maintained so packets can be committed as soon as they are passed to the other link controller.

Packets that do not have any ordering requirements may leave the Rx buffers in a different order than they reached them, both between and within virtual channels. In general, the Rx buffers select a packet choosing the oldest non-blocked packet in each channel to a given destination.

# 3.3 HyperTransport Address Map

HyperTransport implements a single flat 40-bit address space for all accesses. All address spaces that can be reached from HyperTransport are mapped into this space. The HyperTransport PCI bridge checks addresses on incoming packets in each space for subranges that it accepts.

#### 3.3.1 Memory Mapped Space

The HyperTransport specification places Memory Mapped Space in the address range of 00\_0000\_0000h to FC\_FFFF\_FFFFh. The HyperTransport PCI bridge accepts two ranges within this space, as enabled by MemSpaceEn in the Command (Cmd) CSR, consisting of the following:

- · Memory Space, defined by the MemBase and MemLimit CSRs.

- Prefetchable Memory Space, defined by the PrefMemBaseUpper/ PrefMemBase and PrefMemLimitUpper/PrefMemLimit CSRs.

Setting the VgaEn bit in the BrCtrl CSR creates the additional window of 00\_000A\_0000h – 00\_000B\_FFFFh, which is also accepted. The HyperTransport PCI bridge never does prefetching to PCI, so the prefetchable/nonprefetchable attribute of these ranges does not matter. RdSized requests to these ranges result in MemRd requests on the PCI bus. WrSized requests to these ranges result in MemWr requests on the PCI bus. If above 4 GB, addresses are passed straight through as a DAC.

## 3.3.2 I/O Space

The HyperTransport specification places PCI I/O space in the address range of FD\_FC00\_0000h to FD\_FDFF\_FFFh. The HyperTransport PCI bridge strips the top 15 bits off of addresses in this range.

- If enabled by I/OSpaceEn in the Cmd CSR, the HyperTransport PCI bridge accepts requests that fall

in the range defined by the I/O Base and I/O Range Base Upper, and I/O Limit and I/O Range Limit

Upper CSRs.

- If set, the IsaEn bit in the Bridge Control CSR creates a series of holes (the top 768 bytes of each 1 KB block in the low 64 KB) in this space that the HyperTransport PCI bridge does not accept.

- Setting the VgaEn bit in the Bridge Control CSR creates an additional set of windows (all addresses in the low 64 KB where the bottom 10 bits are in the ranges 3B0h – 3BBh or 3C0h – 3DFh) which the HyperTransport PCI bridge accepts. Accepted RdSized requests result in loRd requests on the PCI

bus, and WrSized requests result in IoWr requests, with the bottom 25 bits of the HyperTransport address passed through. Bits 31:26 are 0.

## 3.3.3 Configuration Space

The HyperTransport specification places PCI configuration space in the address range of FD\_FE00\_0000h to FD\_FFFF\_FFFFh. Address bit 24 identifies requests as Type 0 or Type 1 configuration requests.

- Type 0 requests are accepted and routed to the HyperTransport PCI bridge internal configuration registers if their device number (bits 15:11) matches the value of BaseUnitId in the HyperTransport Command CSR.

- Type 1 requests are accepted if their bus number (bits 23:16) falls within the range defined by the Secondary Bus Number and Subordinate Bus Number CSRs, inclusive. Type 1 requests are routed to PCI, as ConfigRd or ConfigWr cycles.

A Type 1 request with a bus number that exactly matches the Secondary Bus Number CSR becomes a PCI Type 0 configuration request, with AD[deviceNumber + 16] set.

Type 1 requests with a bus number greater than Secondary Bus number but less than or equal to Subordinate Bus number are passed on to PCI as Type 1 configuration cycles. Bits 23:2 of the address are left unchanged. The HyperTransport PCI bridge does not support the Type 1 configuration to special cycle mapping.

## 3.3.4 Interrupt Space

The HyperTransport specification places interrupt space in the address range of FD\_F800\_0000h to FD\_F8FF\_FFFh. The HyperTransport PCI bridge only accepts End of Interrupt (EOI) requests in this range, which should always be broadcasts. These EOI requests are routed to the interrupt controller.

# 3.4 HyperTransport Packet Transmission

The HyperTransport packet generator logic is essentially a large arbiter/multiplexer that formats and combines packets from each of the three virtual channels issued from within the HyperTransport PCI bridge. The output stream is combined with the stream of packets forwarded through the HyperTransport PCI bridge from the far HyperTransport link receiver's Rx buffers. This later multiplexing is also used to insert NOP/buffer release messages to the transmitter on the link's other end.

Packet transmission is paced by the transmit buffer counters maintained in each virtual channel for both command/address and data, as the HyperTransport specification describes. These counters are decremented as packets are transmitted and incremented as buffer release messages are received from the transmitter at the link's other end. Transmit buffer counters can be throttled using the txBufCountMax CSR (C8h and CCh).

## 3.4.1 Packet Insertion

To prevent devices close to the host bridge from starving devices further out in the chain of bandwidth, the HyperTransport PCI bridge implements the packet insertion fairness algorithm described in the HyperTransport specification. This algorithm throttles the insertion rate of packets from the HyperTransport PCI bridge relative to packets being forwarded and attempts to balance the packet insertion rates of all devices on the chain.

Insertion of buffer release messages is forced, even when the outgoing transmission stream is busy. Forcing allows traffic to flow to the HyperTransport PCI bridge continuously while maintaining a relatively small number of Rx buffers. The HyperTransport PCI bridge forces a buffer release message as soon as possible when an Rx buffer is freed, subject to the requirements of the HyperTransport protocol. The frequency of buffer release messages is limited under the control of the LdtTx CSR to prevent them from occupying too much bandwidth in a busy stream. Throttling buffer releases clumps the released messages together and raises their efficiency.

In a single-hosted HyperTransport chain, the HyperTransport PCI bridge may be at the end of the chain furthest from the host and therefore have no downstream link connection. In this case, packets are routed to the End of Chain (EOC) logic in the unconnected link interface. The EOC logic drops responses and posted

requests and generates Non-Existent Access (NXA) Error responses back into the receiver for nonposted requests. These error responses then get forwarded back to the other HyperTransport link interface and back to the requesting device. Error logging for the dropped packets occurs in the LinkCtrl CSRs (44h and 48h).

# 3.5 Outbound Transactions

Outbound transactions to the HyperTransport PCI bridge are those accepted from the HyperTransport chain. All outbound requests go first from the HyperTransport link interface on which they are received to the Outbound Request Controller (ORC). This controller is responsible for issuing the request to the appropriate destination functional unit and for tracking the request state while it is outstanding.

The controller has four buffers which allow state tracking for up to four outstanding requests. If multiple requests are outstanding in the controller at once, it rotates among them in round-robin fashion to issue or reissue them. When the ORC file fills, subsequent requests back up to the HyperTransport Rx buffers. Since the ORC doesn't guarantee ordering, the HyperTransport Rx buffers must not issue the second in an ordered pair of transactions until the first has completed.

The ORC is also responsible for managing space in the PCI response data buffer. All outbound nonposted requests, regardless of destination, must be allocated space in the response data buffer before they can be accepted from the HyperTransport Rx buffers by the ORC. The data buffer is not large enough to allocate space for all four requests tracked in the ORC's buffers. This guarantees that the Outbound Request Buffers are never filled with nonposted requests, and posted requests can always get in. This, in turn, provides the deadlock-avoidance guarantee required by the PCI Local Bus specification (nonposted requests are never allowed to block posted requests).

As requests complete at their destinations that fact is signaled back to the ORC which allows the request buffer to be retired. If the request was nonposted, the transaction will require generation of a response to the host. OCR considers posted transactions as complete when the request completes at its destination and the buffer is retired. Nonposted transactions are complete when the response packet is issued to the HyperTransport transmit interface from which the request was received.

#### 3.5.1 CSR Master

All configuration accesses to the HyperTransport PCI bridge CSRs are handled by the CSR master engine. The CSR master engine controls the registers in multiple CSR slaves. These slaves are dispersed around the chip so that registers can be physically close to the functions that they control or monitor. The partition between slave modules is invisible from software's point of view.

The CSR master can handle a single CSR read or write at a time. All CSR accesses complete in a fixed amount of time once they reach the master. Data returned from CSR reads is placed in the PCI response data buffer.

The HyperTransport PCI bridge implements a single-function PCI bridge header with a slave HyperTransport capability block. Because the HyperTransport PCI bridge primary bus is not PCI, not all bits of the standard PCI header are used, as the HyperTransport specification defines. The HyperTransport PCI bridge PCI device number is contained in the BaseUnitId CSR in the HyperTransport capability block and is written as part of the HyperTransport initialization sequence.

Only accesses that fit within a 32-bit aligned block are supported. Accesses that span multiple 32-bit blocks receive an HyperTransport error response, equivalent to a PCI target abort. All registers not listed in the CSR descriptions are considered reserved. Reserved bits return undefined values when read and have undefined results if written with values other than those that were read out. Writes to undefined registers have undefined results.

#### 3.5.2 PCI Outbound Transactions

Outbound requests to PCI are handed to the PCI interface to be driven out to the bus. Write data comes from the Rx data buffers. Read data is returned from the bus and placed in the PCI Response Data Buffer.

The PCI interface can be enabled to perform fast back-to-back transactions. When the bus is configured as 64 bit at reset (PCI\_AD[14]), the interface automatically asserts P\_REQ64\_N on all transactions for which it is legal. When the bus is configured as 32 bit, the interface automatically shuts down both its input and output buffers for P\_AD[63:32], P\_CBE\_N[7:4], P\_REQ64\_N, P\_ACK64\_N, and P\_PAR64.

The PCI interface supports Type 0 PCI configuration cycles to device numbers 0 through 15. P\_AD[31:16] are driven with a one-hot encoding during these configuration cycles, with bit 16 asserted for accesses to device number 0. This logic assumes that one P\_AD bit is connected to the IdSel# pin on each PCI slot through a series resistor on the board. If the resistor increases the settling time of IdSel# to the point at which it doesn't make timing in one PCI cycle, the IdSelCharge field of the PCI Control register may be set to a nonzero value to provide more time. Setting the IdSelCharge field of the PCI Control register to a nonzero value opens a window where the HyperTransport PCI bridge may lose control of the PCI bus because of its failure to drive P\_FRAME\_N immediately, which may have implications about forward progress.

If a request is retried or disconnected on the PCI bus, that fact is reported back to the ORC. The controller finishes any data movement associated with the disconnected transaction and then reissues the request from the point of disconnection. It continues to reissue a request until it completes or until the retry timer for the request expires. Because the ORC can handle multiple outstanding requests, transactions repeatedly retried or disconnected may be reordered or interleaved.

## 3.5.3 PCI Response Data Buffer

The PCI response data buffer contains read data returned from outbound reads to either the PCI interface or the CSR master. This data buffer is a RAM holding 48 DW of data, 16 DW each for three HyperTransport read requests.

Because multiple reads may be in progress to the PCI and CSR interfaces at one time, with their returning data getting interleaved by PCI disconnects, this cannot be a FIFO structure. Each buffer accumulates data for its request until all requested DW are returned. This data is then combined with response header information from the ORC to form the response packet for the operation.

Once the response is issued, the buffer is retired. Nonposted write requests still occupy space in the response data buffer, even though they have no read data.

#### 3.5.4 End of Interrupt

When an interrupt is configured as level sensitive, upstream interrupt logic must respond to an interrupt request packet with an end of interrupt (EOI) packet. Until the EOI packet is received by the HyperTransport PCI bridge, no new interrupt request packets will be generated by that interrupt pin.

Note: See Interrupt Generation, Section 3.6.12.

#### 3.6 Inbound Transactions

Inbound transactions are requests from the PCI bus or interrupt controller across HyperTransport to the host bridge. From there, they are routed to destinations behind the host bridge or reflected peer-to-peer back onto the HyperTransport chain. If the request is nonposted, the transaction also includes the response from the host bridge back to the original requesting unit.

The HyperTransport PCI bridge operates as a PCI target for requests from external PCI devices. All accepted requests are forwarded to the HyperTransport link interface leading to the host. Reads go though the delayed request buffers and are handled on the PCI bus as delayed requests. All writes, regardless of type, are posted into the posted request gueue and allowed to immediately complete on the PCI bus.

#### 3.6.1 PCI Address Map

Accesses on the PCI bus are checked against the following ranges to determine whether the HyperTransport PCI bridge is the target of the access and should assert P\_DEVSEL\_N to accept the request. The HyperTransport PCI bridge makes this determination with medium DEVSEL# timing. When configured as a 64-bit target at power up, the HyperTransport PCI bridge asserts P\_ACK64\_N in response to P\_REQ64\_N for requests it accepts.

Memory Mapped Cycles. The HyperTransport PCI bridge implements a 40-bit space for memory

mapped accesses and decodes DAC accesses for addresses above 4 GB. In Pass1, address bits

above bit 39 are ignored and result in the 40-bit space aliasing through PCI's 64-bit memory mapped

space. In Pass2, any address with a non-zero value in the top 24 bits of the 64 bit PCI address is left

on the PCI bus.

Memory mapped addresses are compared to the range defined by the Memory Range Base Addr and Memory Range Limit Addr CSRs; and the range defined by the Prefetchable Memory Range Base Upper and Prefetchable Memory Range Base Addr, and Prefetchable Memory Range Limit Upper and Prefetchable Memory Range Limit Addr CSRs. If the VgaEn bit in the Bridge Control CSR is set, the address is also compared to the fixed range of 00\_000A\_0000h – 00\_000B\_FFFFh. Addresses that don't fall into any of these ranges are accepted for forwarding to HyperTransport, as long as the MasterEn bit in the Command CSR is set and bits [39:32] <= Fch.

I/O Cycles. The HyperTransport PCI bridge implements a 25-bit space for I/O accesses. In Pass1, address bits above bit 24 are ignored and result in the 25-bit space aliasing through PCI's 32 bit I/O space. In Pass2, the top 7 of the 32 bits must be 0 for the access to reach HyperTransport.

I/O addresses are compared to the range defined by I/O Range Base Upper and I/O Base, and I/O Range Limit Upper and I/O Limit CSRs. If the IsaEn bit in the Bridge Control CSR is set, a series of holes are created in this range at the top 768 bytes of each 1 KB block in the low 64 KB. If the VgaEn bit in the Bridge Control CSR is set, I/O addresses in the low 64 KB have their bottom 10 bits compared to the ranges 3B0h – 3BBh and 3C0h – 3DFh. Accesses that miss all the enabled ranges are accepted for forwarding to HyperTransport, as long as the MasterEn bit in the Command CSR is set.

Configuration and Special Cycles. The HyperTransport PCI bridge never acts as a target for configuration or special cycles on the PCI bus.

#### 3.6.2 PCI Posted Write Queue

The HyperTransport PCI bridge responds as a PCI write target to PCI Memory Write, Memory Write Invalidate, and I/O Write commands. All of these writes are posted to the HyperTransport chain. The HyperTransport PCI bridge never responds to Configuration Writes. A total of 192 bytes of buffering for posted write data is provided.

Memory Write and Memory Write Invalidate commands stream data into the chip, disconnecting either on 4-KB boundaries or when all of the internal buffer space is filled. The HyperTransport PCI bridge generates the largest HyperTransport write operations possible, issuing them continuously as the data for each write is received from PCI.

As the bandwidth of HyperTransport exceeds the bandwidth of PCI, it is expected that the internal buffers will not fill and memory writes will proceed continuously at the full bandwidth of the PCI bus.

I/O writes are not allowed to stream and always disconnect after a single data beat on the PCI bus (32 bits). Each I/O write is issued to HyperTransport as an independent request.

## 3.6.3 PCI Delayed Request Buffers

The HyperTransport PCI bridge acts as a PCI read target for PCI Memory Read, Memory Read Line, Memory Read Multiple, and I/O Read commands. The HyperTransport PCI bridge never responds to configuration read or interrupt acknowledge accesses. All supported read transactions are implemented as PCI delayed reads.

Incoming reads are assigned to a delayed request buffer. There are four delayed request buffers, enabled under CSR control, allowing up to four PCI read requests to be in progress at one time. If no delayed request buffers are free, the incoming request is retried until one is available. Once the request is assigned to a buffer, the interface continues to retry it on the PCI bus while read requests are issued to the HyperTransport interface.

#### 3.6.4 Prefetching

The HyperTransport PCI bridge supports a variety of prefetching options configured under CSR control using the Read Control CSR (62h:60h), however:

- · I/O reads are never prefetchable.

- MemRdLines and MemRdMult may have prefetching individually configured.

- For systems in which MemRds are known to be side-effect free, MemReadPrefEn can be set to enable prefetchable behavior for MemReads using the same parameters as MemRdLines.

- PrefEn can be used to globally enable or disable all prefetching.

- Nonprefetchable reads always request only the bytes required to satisfy the initial data beat of four or eight bytes on the PCI bus, which may result in either one or two HyperTransport requests.

Transactions for which prefetching is enabled issue a HyperTransport read for the remainder of the 64-byte aligned block containing the original request. These transactions also issue HyperTransport reads for the zero to seven complete 64-byte blocks following, as determined by the Read Control CSR. The total number of reads that may be outstanding to HyperTransport at one time is limited by the Outbound Data Buffers.

When multiple reads to HyperTransport are issued for a single PCI read request due to prefetching or due to clear byte enables in a 64-bit nonprefetchable read on a 64-bit bus, each HyperTransport request is referred to as a subrequest of the PCI request. Each Delayed Request Buffer can track up to 8 subrequests at once. The total number of configured subrequests (number of enabled delayed request buffers \* (the maximum number of subrequests each, rounded up to the next power of 2)) must not exceed the number of entries in the Outbound Data Buffers.

## 3.6.5 SrcTags

The SrcTag for each HyperTransport read request is formed by concatenating the delayed request buffer number with the number of the HyperTransport subrequest being issued by that buffer and adding a leading 0 (zero) bit.

- If three or four delayed request buffers are in use, a maximum of four reads may be outstanding for each one. The subrequest number is two bits. The delayed request buffer number is two bits.

- If only one or two delayed request buffers are in use, a 3-bit subrequest number is used. Only one bit of delayed request buffer number is needed and the top bit is dropped.

Either way, five bit srcTags are generated in the range of 00h – 0Fh.

#### 3.6.6 Sequences

HyperTransport subrequests that are part of the same PCI request must be tagged with a matching nonzero seqld to guarantee ordering at the target. This 4-bit seqld is formed by concatenating a leading 1 (guaranteeing a nonzero result) with the 2-bit delayed request buffer number and one bit that toggles for each occupation of the delayed request buffer. The concatenation prevents consecutive PCI reads from being issued with the same seqld and appearing to have HyperTransport ordering requirements.

## 3.6.7 Read Responses

As the read responses return from HyperTransport, the data is stored in the Outbound Data Buffers. Even though sequenced requests are guaranteed to reach the target in order, responses may be received from the target out of order. When all data from the first HyperTransport requests is received (the amount required is controlled by the InitCount fields of the Read Control CSR), the PCI interface ceases retrying the request. Read data is supplied from the buffers when the request is next reissued. Data streams to the PCI bus until the transaction is disconnected by the PCI master or until the next data required is not present in the Outbound Data Buffers.

# 3.6.8 Continuous Prefetching

If continuous prefetching is enabled in the Read Control CSR, the HyperTransport PCI bridge issues further ascending read requests to fill buffers as they drain (up to a 4-KB page boundary) in an effort to make sure required data is always available. Otherwise, the transaction is disconnected as soon as all data from the initial reads is returned to the PCI bus.

#### 3.6.9 Transaction Disconnects

Read transactions may be disconnected by the bridge when required data is not available in time, or by the master. The Delayed Request buffer remains in use until all outstanding HyperTransport prefetch requests receive their responses; then it is retired and any leftover data discarded. Each delayed request buffer also has an associated discard timer loaded with one of two values determined by the Secondary Discard Timer bit (9) of the Bridge Control CSR (3Eh) when the data is received from HyperTransport. If this timer expires before the data is called for by the PCI master, the data is discarded and the buffer retired.

#### 3.6.10 Performance Variables

The following PCI inbound read performance characteristics can be tuned for best performance in a given system architecture or traffic load by using fields in the Read Control CSR. Independent prefetch controls are also provided for both MemRdMult and MemRdLine commands. If prefetching is enabled for MemRd commands, the MemRdLine values are used.

- PCI Delayed Request. The PCI Delayed Request field controls the number of PCI requests that can

be fetching data at one time. Having multiple delayed requests generally reduces average latency on

the PCI bus by fetching for multiple PCI requests simultaneously. However, setting the number of

fetches too high may interfere with continuous prefetching.

- When the number of fetches is set too high, a large number of reads may be sent to HyperTransport

due to other PCI reads between the initial fetches and the ones generated as the data buffers drain to

PCI. If these subsequent fetches backup far enough, they may not succeed in returning data in time to

keep the burst from ending on the PCI bus at which point their data might be discarded.

- Ideal Prefetch Count. If the available HyperTransport bandwidth exceeds the PCI bandwidth, there is an ideal prefetch count for large transfers. The ideal prefetch count is determined by dividing the number of bytes that can be transferred on the PCI bus in the round-trip read latency by 64 (the number of bytes in a prefetch request).

- The number of bytes that can be transferred on the PCI bus depends on the bus characteristics: 32 or 64 bit, 33 or 66 MHz, or 25 or 50 MHz.

- Round-trip read latency depends on the latency of and distance to the target.

- With continuous prefetching enabled, the HyperTransport PCI bridge will be able to keep up with an arbitrary length burst.

- InitCount. If the available HyperTransport bandwidth is less than the PCI bandwidth, there is no ideal

prefetch count. HyperTransport will eventually be forced to disconnnect on a long burst because it will

be out of data. Disconnects like this waste PCI bandwidth and waste HyperTransport bandwidth by

discarding the prefetched data.

- In this case, setting the InitCount above zero will require more data to be on hand before the

transaction is allowed to reconnect on PCI. The nonzero setting increases utilization of

HyperTransport bandwidth at some cost in PCI latency, but reduces the number of wasteful

disconnects. Continuous prefetching should also be disabled since the extra prefetches would

probably not arrive in time to be used and would likely be discarded.

## 3.6.11 Outbound Data Buffer

• The HyperTransport PCI bridge contains a central data buffer (sixteen 64-byte entries) for the accumulation of read response data to return to the PCI bus. Entries in the buffer are assigned to PCI reads by the same algorithm used to assign srcTags—the bottom four bits of the srcTag are the entry number. Because of this one-to-one correspondence, no separate mechanism for allocation of data buffers is required. Data from returning HyperTransport responses is loaded into the buffer based on the srcTag in the response header and drained out to the PCI bus when the delayed request reconnects.

#### 3.6.12 Interrupt Generation

The HyperTransport PCI bridge interrupt controller consists of four blocks of generic interrupts, four interrupts per block, and one set of special interrupts. In *Pass2*, the special interrupts are not available.

Each block, and the interrupts below that block, are configured by CSRs. Interrupt configuration options include: enable, edge versus level sensitivity, polarity, and vector ID.

An incoming interrupt is first synchronized to the core clock domain and masked with its CSR enable bit to set the interrupt's bid in the Interrupt Request Register (IRR). A round-robin arbiter will then examine each IRR bit and forward requests to the primary bus logic, setting its In Service Register (ISR) bit. New interrupts from that pin will not be accepted as long as the ISR register is set.

- For edge sensitive interrupts, the ISR bit is cleared as soon as the primary interface logic accepts the inbound interrupt request.

- For level interrupts, the ISR bit is not cleared until an End of Interrupt (EOI) packet is received with a vector ID matching the ISR.

- All interrupts and interrupt blocks are disabled at reset and must be enabled by software.

- The ISR can also be monitored via the Control Status Register (CSR).

## 3.6.13 Interrupt Diagnostic Mode

To simplify debugging interrupt software and hardware, each interrupt may be stimulated and monitored via CSR reads and writes (see the Interrupt Diagnostic Register for CSR details). Writing a 1 to the Initiate field of the CSR will generate an interrupt on the interrupt line in the Pin Number field. The ISR bit may be observed by monitoring the Active field of the same CSR.

Note: The Active field is always for the CSR indicated by the Pin Number field.

# 3.7 PCI Arbiter

The HyperTransport PCI bridge includes a PCI arbiter. This arbiter is an independent unit. The Hyper-Transport PCI bridge internal PCI request and PCI grant signals connect to pins as P\_REQ\_OUT\_N and P\_GNT\_IN\_N. It is possible to either use this arbiter or to bypass it and use an external arbiter.

The HyperTransport PCI bridge arbiter contains two round-robin arbitration groups: P\_REQ0\_N and P\_PREQ\_N; and P\_REQ1\_N through P\_REQ5\_N. In Pass2, P\_PREQ\_N is not available.

Arbitration is shared equally between the two groups. Within each group, arbitration is shared equally between the requests. Generally, P\_REQ\_OUT\_N would be attached to P\_REQ\_N and P\_GNT\_IN\_N attached to P\_GNT0\_N, because this causes the arbiter to share equally between inbound and outbound PCI traffic.

When there are no requests present, the arbiter either parks the bus at the last grant or (based on a CSR bit) at P GNT0 N which is presumed to be the HyperTransport PCI bridge internal requester.

The PCI Control CSR ParkMaster bit allows configuration of the internal PCI Arbiter parking.

# 3.8 Reset

# 3.8.1 Cold Reset

Cold reset of the HyperTransport PCI bridge is caused by the deassertion of the L\_POWER\_OK pin. At power-on, L\_POWER\_OK must remain deasserted until power and clocks are stable for at least 1 ms. L\_RST\_N must be asserted before L\_POWER\_OK deasserts and remains asserted for at least 1 ms following.

Cold reset results in the initialization of all internal state, including the loading of internal registers from strapped PCI bus pins and the SRI (Serial ROM Interface). The PCI bus is held in reset until the deassertion of L\_RST\_N.

#### 3.8.2 Warm Reset

Warm reset of the HyperTransport PCI bridge is caused by the assertion of L\_RST\_N while leaving L\_POWER\_OK asserted. Once asserted, L\_RST\_N must remain asserted for at least 1 µs.

Warm reset results in the initialization of most internal state, with the exception of state loaded from PCI bus sampling or the external SROM interface, and persistent error state. The PCI bus is held in reset until the deassertion of L\_RST\_N.

#### 3.8.3 Serial ROM Initialization

There are 224 bits loaded from a Serial Read Only Memory (SROM). The SRI (Serial ROM Interface) allows loading of configuration information into the HyperTransport PCI chip during reset.

On the rising edge of L\_POWER\_OK, the state of P\_AD[1] is observed. If it is high, configuration information is loaded into the HyperTransport PCI chip from an external SROM.

Once L\_POWER\_OK is asserted, the SRI state machine begins to drive SROM\_SCK to the external SROM. The state machine expects data to be valid by the falling edge of SROM\_SCK. The state machine runs, shifting in data until all configuration information is read.

If P\_AD[1] is low during the assertion of L\_POWER\_OK, internal SIP values are used for all configuration bits and no data is loaded.

## 3.8.4 Reset Configuration

In addition to loading configuration information from the SIP, information may also be loaded into the HyperTransport PCI bridge at reset from the PCI AD bus, P AD[63:0].

| Signal                 | I/O         | Definition                                                                                         |  |

|------------------------|-------------|----------------------------------------------------------------------------------------------------|--|

| minRstCnt              | P_AD[31]    | Reserved for API NetWorks. Must be tied to 0.                                                      |  |

| dbgSelCtl              | P_AD[30]    | Use SROM or CSR for dbg selects. 0 = SROM 1 = CSR                                                  |  |

| L0_clkSel              | P_AD[29:27] | Link0 Clock Divider Select                                                                         |  |

| L1_clkSel              | P_AD[26:24] | Link1 Clock Divider Select                                                                         |  |

| coreSel                | P_AD[23:22] | Core Clock Divider Select                                                                          |  |

| sri0_LdtSyncPtrCtlDflt | P_AD[19]    | Link0 Sync Pointer Control values used only when external SROM is not being loaded. 1=Sync 0=Async |  |

| sri1_LdtSyncPtrCtlDflt | P_AD[18]    | Link1 Sync Pointer Control values used only when external SROM is not being loaded. 1=Sync 0=Async |  |

| monitorMode            | P_AD[17]    | 1=Enable monitor mode<br>0=Normal mode                                                             |  |

| monModeLink0Sel        | P_AD[16]    | 0=Link1<br>1=Link0                                                                                 |  |